Other Parts Discussed in Thread: LMK04832

Hi,

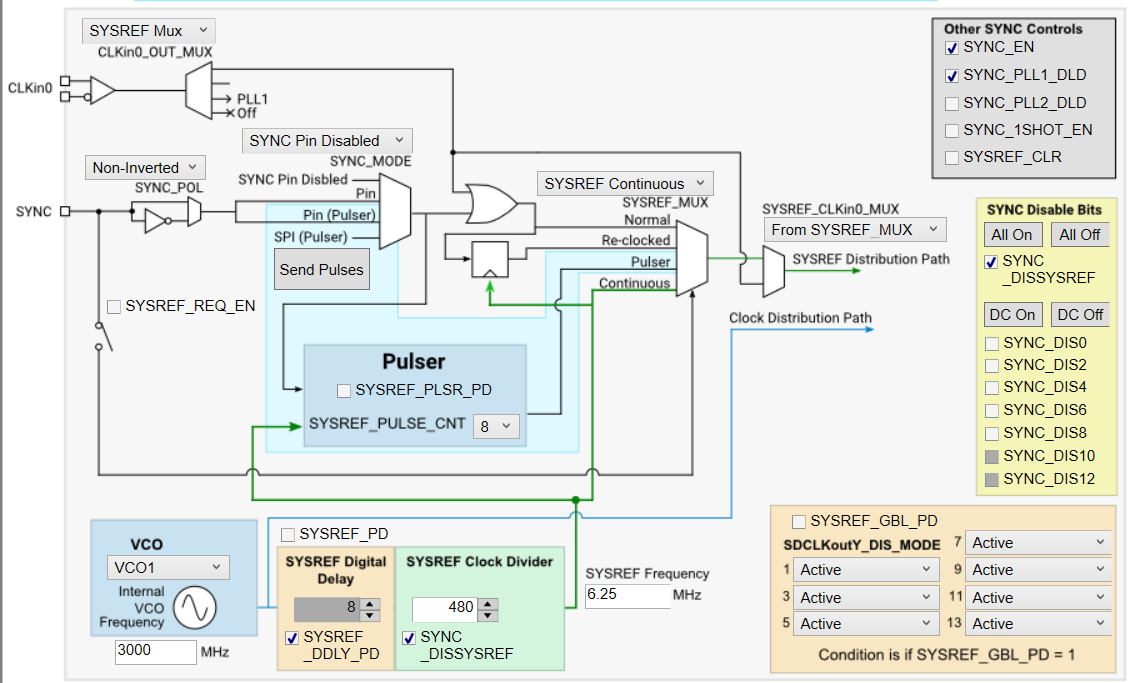

i am planning to set the LMK04828 in nested ZDM mode + reclock clkin0 for sysref.

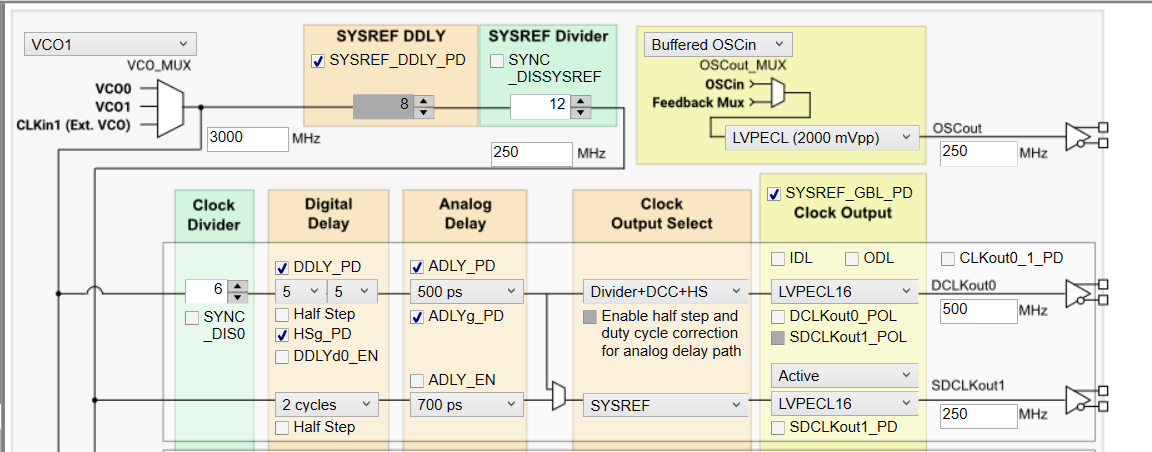

Below in my frequency plans:

Dclk = 250MHz

SDclk = 6.25MHz

Clkin1 = 250MHz

clkin0 = 6.25MHz

i set the internal SYSREF divider to output 250 MHz and use it as ZDM feedback for PLL1. To get the SDCLK, i wanted to configure the SYSREF muxes to forward CLKin0 to SDCLKoutY as the figure attached below. however, i am not able to do so in TICS. the source of SDCLKout is from either SYSREF divider or DCLK.

Can you advise how to configure correctly?

Thanks.