Hello,

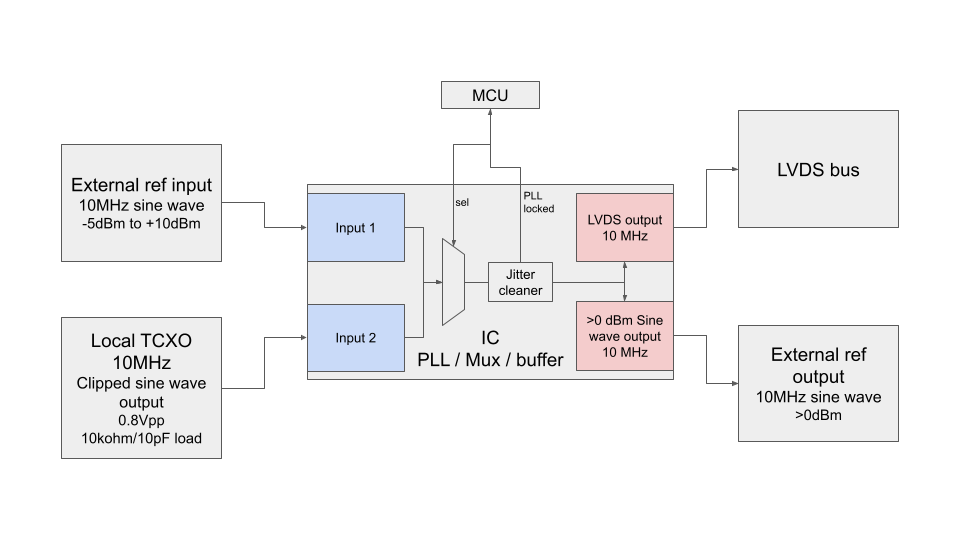

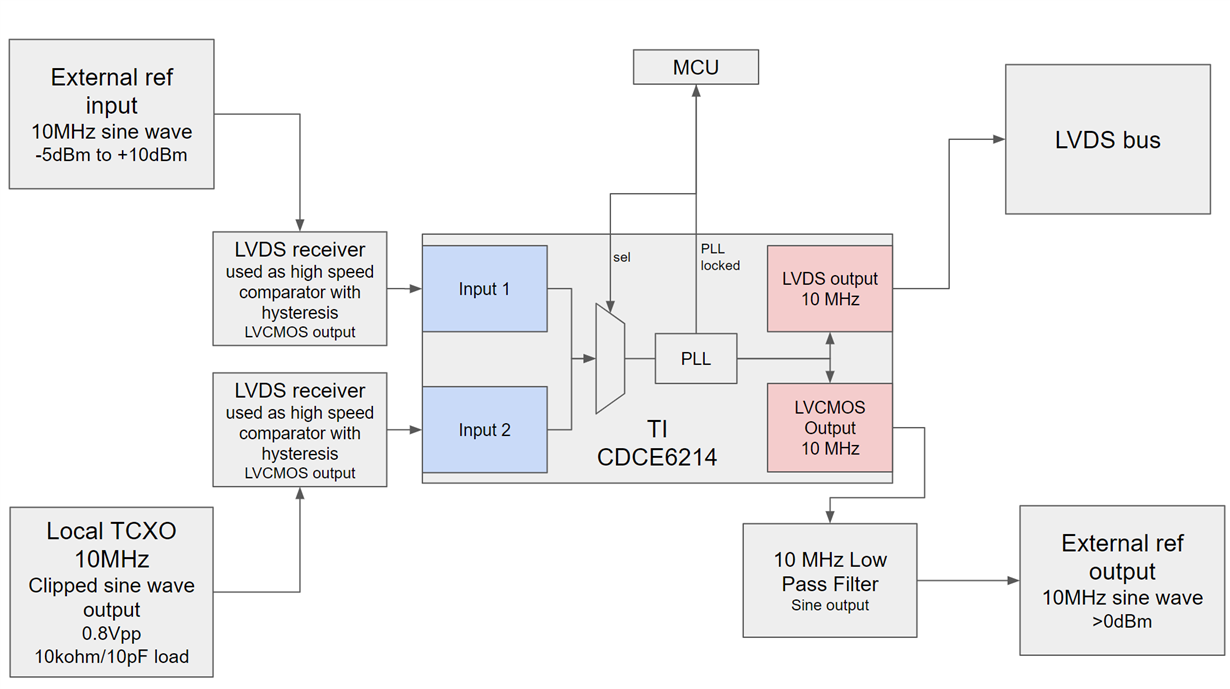

I am working on a device which takes as an input an external 10 MHz clock ref or a local oscillator. This device should generate a 10MHz sine wave output as well as an LVDS clock.

Could you please recommend a part or parts that can correspond to the following block diagram please?

Thank you in advance,

Victor