Other Parts Discussed in Thread: LMX2492, LMK04816, LP5912

Hi,

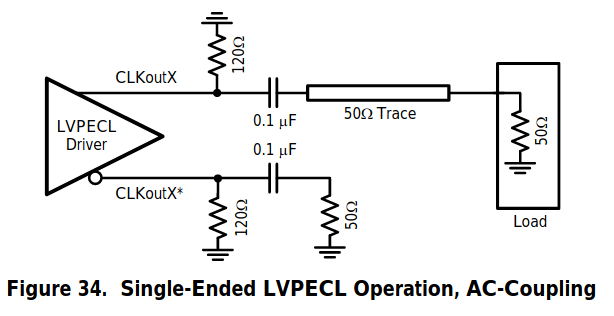

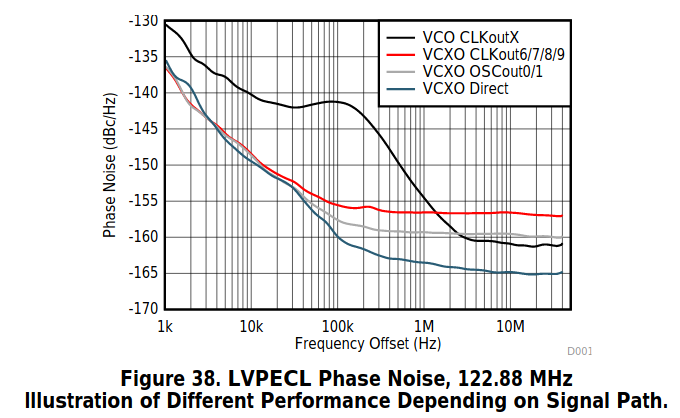

The LMK04906 datasheet gives a phase noise plot on page 108 comparing OSCout/CLKout VCXO and VCO phase noise performance. Is this measurement taken as described on page 91 (Figure 34)? I.e. is this figure measured single-ended or differentially (using an external balun)?

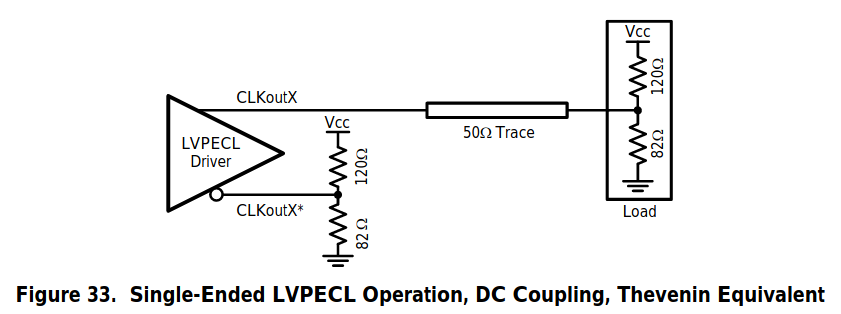

We designed the LMK04906 into a product but we cannot achieve the same noise floor performance of the OSCout/CLKout output as given in the datasheet. However we are using the LVPECL OSCout0 output as two single-ended outputs as shown in Figure 33 (page 91). We are now questioning whether we can actually do something about it.

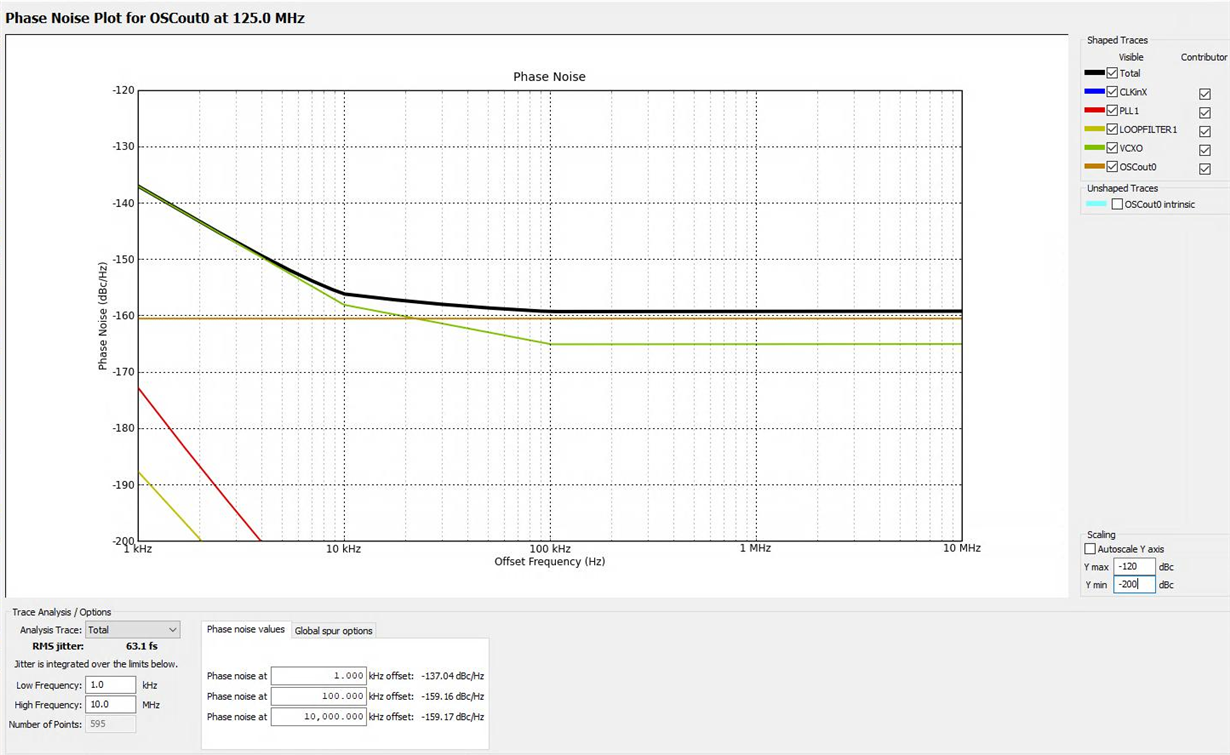

We are able to reach about -150dBc/Hz as the noise floor. The reference clock is a 125 MHz Ultra Low-Noise Crystal Oscillator with LVCMOS Output (1kHz: -137dBc/Hz, 10kHz: -158dBc/Hz, 100kHz: -167dBc/Hz, floor: -169dBc/Hz). According to the simulation we should reach close to -159dBc/Hz on the OSCout0 output with LVPECL standard and divider bypassed.

If the simulated figure is realistic in our single-ended scenario, any hints on what we could try to reduce the noise floor? Which supply voltage pins can raise the noise floor of the chip?

Best Regards and Thank you in advance