Other Parts Discussed in Thread: LMX2594

Tool/software: WEBENCH® Design Tools

Hello Forum,

I think there is a bug in the TICS Pro V1.7 software with a LMX2572 device and the "Support Request" people can't help about this!

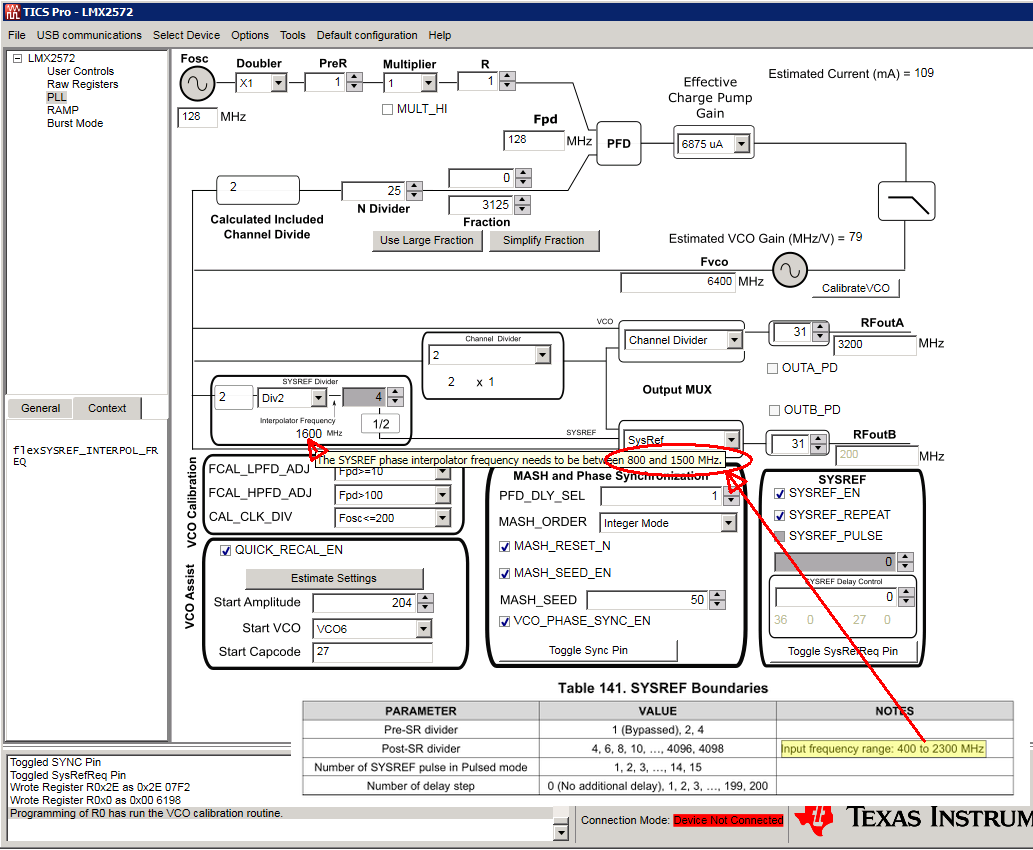

There is a discrepancy between datasheet and software tooltip about the Post-SR divider input frequency range.

Please have a look at the following picture from the software and the included datasheet table:

Goal is to use the PLL in Integer mode (for a JESD204B application) with or without phase adjustment/shift (of course is a MASH ORDER >= 2 for the latter one necessary) and additional SYSREF shifting in repeating-mode.

By the way: is the SYSREF divder value (and therefore the limits) important for the SYSREF_REPEAT mode, on the other hand the stepsize depends on the "Pre-SR divider" value?

Best regards