Other Parts Discussed in Thread: LMK00301

hello,

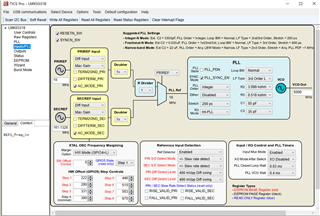

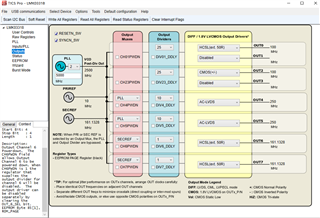

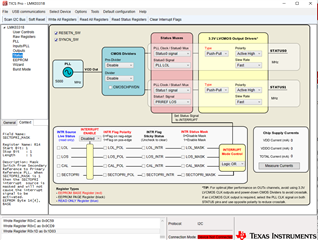

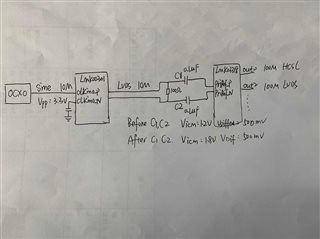

The current project uses the LMK03318 chip and found that the phase-locked loop is unstable. We did a stress test and found that there was a loss of lock within 1-3 hours during the period, and the lock light did not turn on after the loss of lock. It needs to be reconfigured or restarted after power failure. locking.

1. Check the power-on sequence requirements.

2. the wizard in TICS PRO used for frequency point configuration.

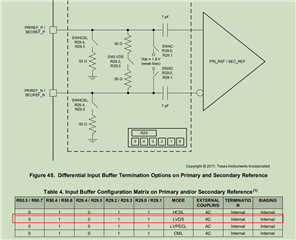

3.the input clock is the LVDS level output by LMK00301, and there is an external AC capacitor.

Not sure why the lock is unstable, do you have any debugging suggestions?

R0 0x0010 R1 0x010B R2 0x0233 R3 0x0301 R4 0x0400 R5 0x0500 R6 0x0600 R7 0x0700 R8 0x0800 R9 0x0900 R10 0x0AA0 R11 0x0B00 R12 0x0CD9 R13 0x0D00 R14 0x0E1D R15 0x0F00 R16 0x1000 R17 0x1100 R18 0x1200 R19 0x1300 R20 0x1455 R21 0x1555 R22 0x16FF R23 0x1703 R24 0x1800 R25 0x195A R26 0x1A00 R27 0x1B28 R28 0x1C08 R29 0x1D03 R30 0x1E00 R31 0x1F58 R32 0x2000 R33 0x2118 R34 0x2278 R35 0x2300 R36 0x2418 R37 0x2510 R38 0x2609 R39 0x2710 R40 0x2809 R41 0x29EC R42 0x2A00 R43 0x2BEC R44 0x2C00 R45 0x2D1A R46 0x2E00 R47 0x2F00 R49 0x3100 R50 0x3256 R51 0x3303 R52 0x3400 R53 0x3500 R54 0x3600 R55 0x3700 R56 0x3806 R57 0x3908 R58 0x3A01 R59 0x3BF4 R60 0x3C00 R61 0x3D00 R62 0x3E00 R63 0x3F00 R64 0x4000 R65 0x4101 R66 0x420C R67 0x4338 R68 0x4401 R69 0x4504 R70 0x4607 R71 0x471F R72 0x4808 R73 0x4900 R74 0x4A64 R75 0x4B00 R76 0x4C00 R77 0x4D00 R78 0x4E00 R79 0x4F00 R80 0x5001 R81 0x510C R82 0x5224 R83 0x5300 R84 0x5400 R85 0x5500 R86 0x5600 R87 0x5700 R88 0x5800 R89 0x59DE R90 0x5A01 R91 0x5B18 R92 0x5C01 R93 0x5D4B R94 0x5E01 R95 0x5F86 R96 0x6001 R97 0x61BE R98 0x6201 R99 0x63FE R100 0x6402 R101 0x6547 R102 0x6602 R103 0x679E R104 0x6800 R105 0x6900 R106 0x6A05 R107 0x6B0F R108 0x6C0F R109 0x6D0F R110 0x6E0F R115 0x7308 R116 0x7419 R117 0x7500 R118 0x7607 R119 0x7701 R120 0x7800 R121 0x790F R122 0x7A0F R123 0x7B0F R124 0x7C0F R129 0x8108 R130 0x8219 R131 0x8300 R132 0x8403 R133 0x8501 R134 0x8600 R135 0x8700 R136 0x8800 R137 0x8910 R138 0x8A00 R139 0x8B00 R140 0x8C00 R141 0x8D00 R142 0x8E00 R143 0x8F00 R144 0x9000 R145 0x9100 R169 0xA940 R172 0xAC24 R173 0xAD00 R12 0x0C59 R12 0x0CD9