Other Parts Discussed in Thread: LMK04832

Hi team,

I got question from customer.

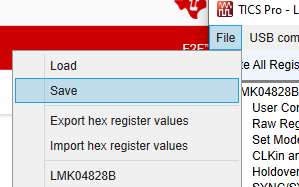

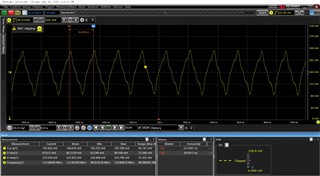

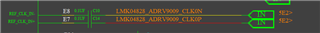

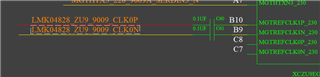

DCLK channel output of LVPECL 1600 format waveform, the output of the actual waveform swing is only more than 100 mV.

Please help with the analysis.

Thanks

Best regards,