Hi~

Customer is under investigating to minimize TLC555-Q1 PWM generator tolerance.

Would you please check below item?

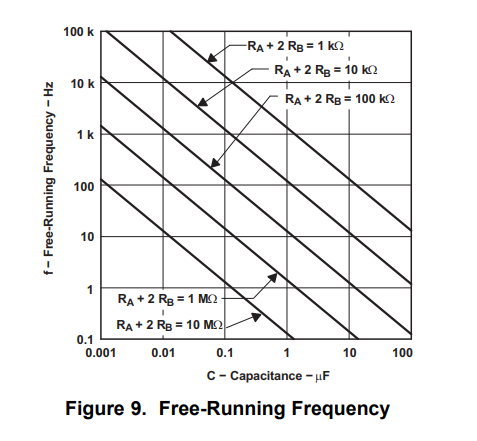

1) Max frequency which can set TLC555-Q1

2) In datasheet, initial error is max 3% under 25deg, how about -40~105deg? can we get that data?

Thanks.