first question :

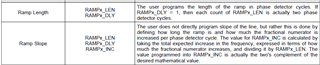

I noticed the description of RAMPx_LEN and RAMPx_INC in datasheet, in every phase detector cycle, the fractional numerator will be increase a certain value witch is

programmed in RAMPx_INC.

and I want to know that whether the PLL will be locked in every phase detector cycle? And HOW if it is locked.

second question:

I try to drive a VCO witch is working at 24GHz with LMX2491, and VCO out put will be through a frequency divider(1/16)first and then go back to LMX2491.

and the frequency of phase detector is 52MHz,loop bandwidth is about 100KHz,VCO output frequency is 24180.01MHz.

Based on my experience, there will be a integer boundary spurs at N * frequency of phase detector(in my design is 24180MHz,offset is 10KHz),but I did not see it .

I want to know WHY.

Which engineer can help me answer my doubts? Thank you very much!