Hello,

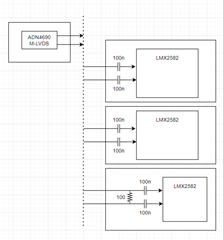

I have a design where I want to use the LMX2582 to generate a ~3.6GHz local clock. The only clock reference for the LMX2582 is from a high-fidelity 10MHz clock available on a backplane, using M-LVDS to distribute this ref clock.

I plan on using the LMX2582 for each of three plug-in cards on this backplane.

I have 2 questions:

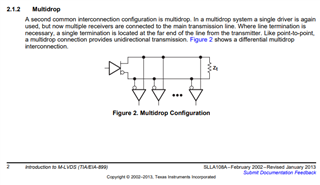

1. What is the best way to terminate this multi-drop LVDS clock, at each of the LMX2582 inputs? I'd prefer not use a LVDS receiver chip, if it's not necessary.

2. Is it not recommended to use such a low frequency clock reference for the LMX2582? If so, what options are recommended for stepping up this high-fi 10MHz reference?

Thanks,

Josh