Hello everyone.

I have correctly configured LMK04610 IC. It has on its two inputs 40MHz from KEYSIGHT 33600A double channel generator. I also used VCXO

ABLNO-V-122.880MHz. Output frequency on nr 5 output is about 10MHz (its convenient to measure), but in a future I will change it to 200MHz.

LMK04610 also correct work on missing first or second input clock. It swich to holdover mode for about 1,5 period of PFD frequency (in my case 80kHz - about 15us)

hold Vcontrol voltage at correct value and swich signal to another source.

And after select another input signal the problem begins. I will just add, that the same situation occurs when resetting the N and R dividers - when I set

PLL1_RDIV_SWRST and PLL1_NDIV_SWRST bits (3 and 4) in 0x57 configuration register.

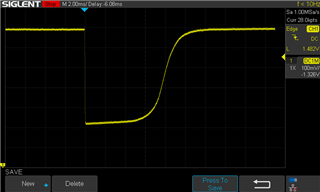

The problem is that PLL1 misses a few clock signals, which can be seen on the control voltage oscillogram. I have attached two oscilloscope screenshots.

As you can see VCO regulation is only on one direction. So VCO phase only change on one side. The integrated control voltage corresponds to a phase change 100ns (it is slightly change when I set another loop parameters). This value corresponds to about 12 clk of 122.88MHz or 4 clk input frequency 40MHz.

My question is that is normal situation? Is any way to initially set R or N divider instead reset? (after holdover R and N dividers are also reset) Is there any other possibility that we could minimalize observed behaviour?