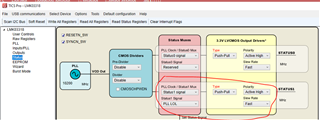

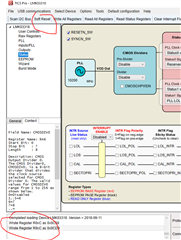

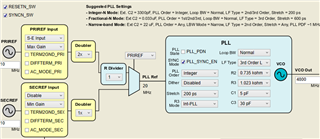

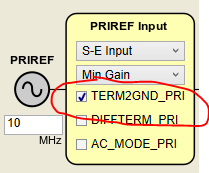

I am using LMK03318 and experiences an instability on the ref clock. It is configured to use PRIREF in single-ended mode, 10MHz, 3V3 signal. PRIREF_N is connected to GND. The PLL is not in lock.

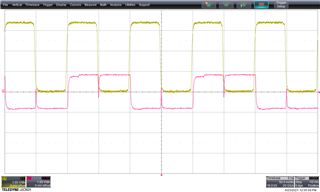

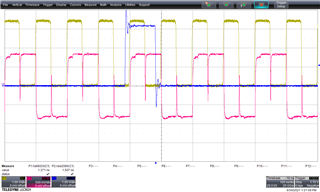

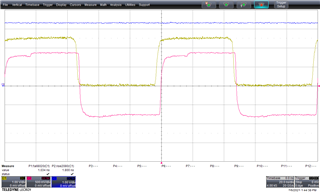

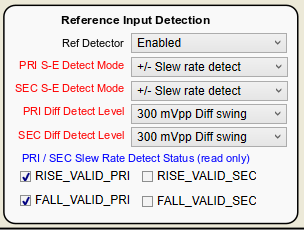

I am routing the PRIREF to Output7 with CMOS(+/HiZ) . The output of this is shown in Red together with the input clock Green. I don't understand what is going on here. It seems like a transition problem and that a flip-flop is involved. When PRIREF is routed to output I was expecting a buffered version only. The input clock is very clean without and reflections or bad flanks(as shown in Yellow). Any idea what is going on and what is wrong?