Other Parts Discussed in Thread: DAC34H84EVM

Dear Team,

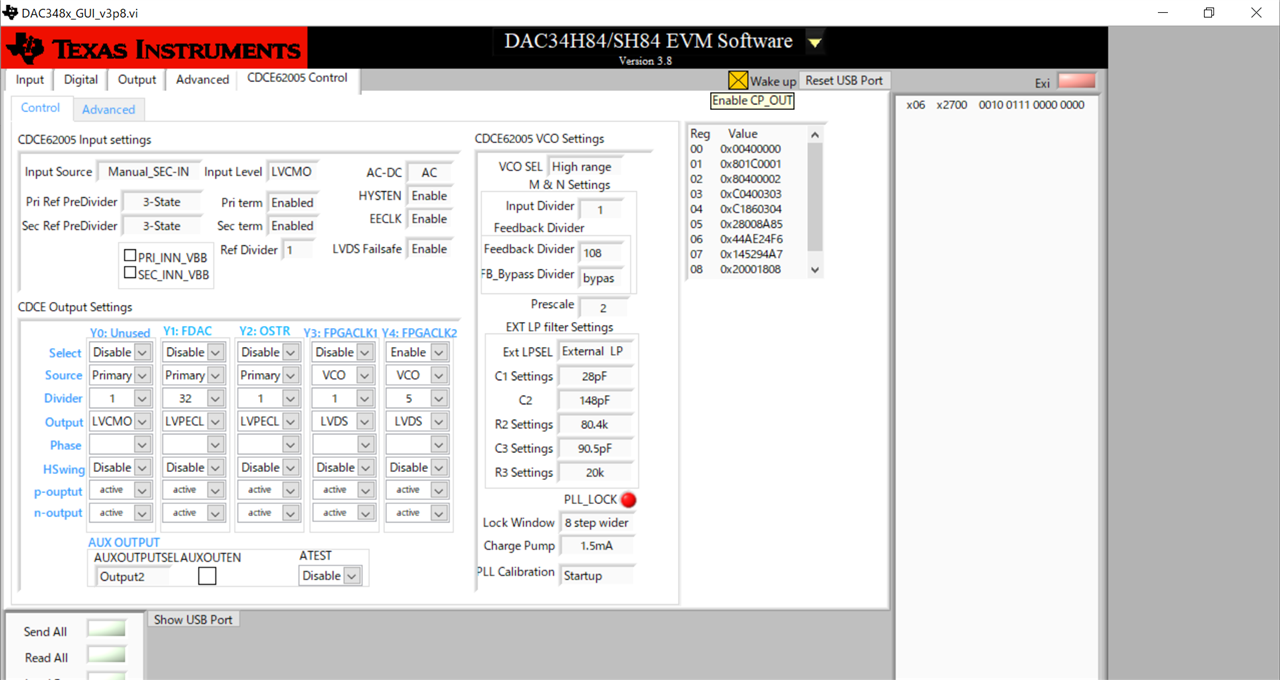

My customer evaluating the DAC34H84EVM with the DAC348x EVM Software GUI. They want to set LVDS clock output as 207.36MHz from J10/J11 pins of the DAC34H84EVM which are U4P/U4N pins of the CDCE62005. The DAC34H84EVM has the 19.2MHz TCXO which is inputted into SEC REF+ pin of the CDCE62005.

They set the GUI as attached, but they got 211.29MHz LVDC clock output from J10/J11 pins of the DAC34H84EVM.

Could you advise them on how to set up the GUI to get the correct 207.36MHz LVDC clock output from J10/J11 pins of the DAC34H84EVM?

CDCE Output Settings, Y4 FPGACLK2 is settings for J10/J11 pins of the DAC34H84EVM.

I look forward to your reply.

Thank you.

Best Regards,

Koshi Ninomiya