Hi team,

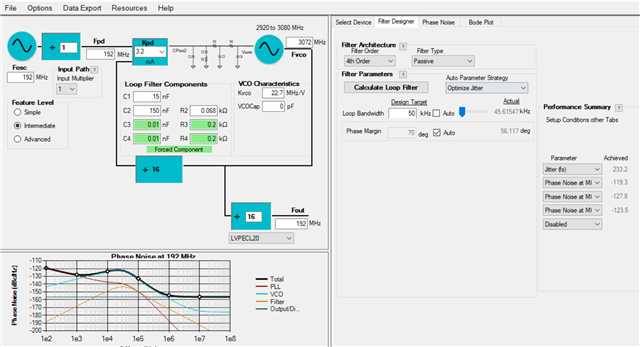

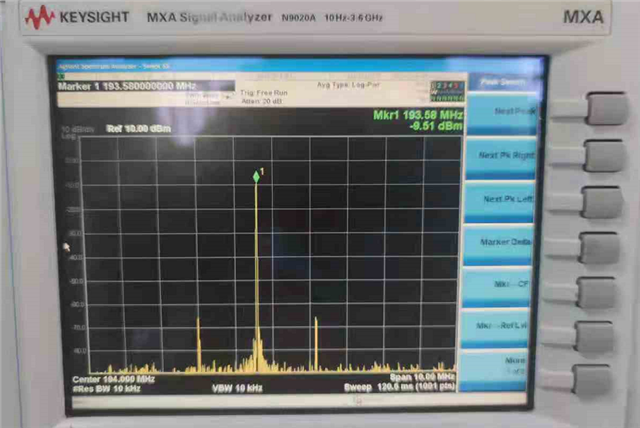

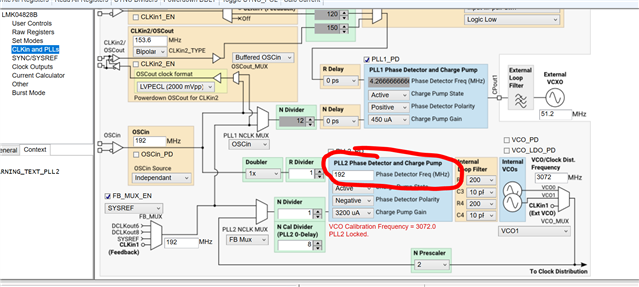

OSCIN input 192MHZ, PLL2 multiplier to 3072MHZ, split output 192MHZ, internal VCO1 used, output frequency inaccurate. What could be the possible cause?

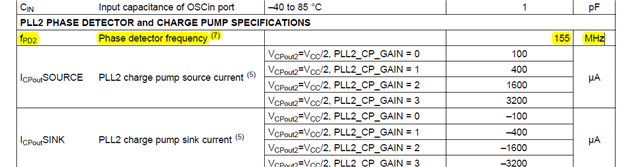

It was later discovered that the fPD2 can only be up to 155MHz, is the output frequency inaccurate because fPD2 is larger than 155MHz?

Best Regards,

Amy Luo