Other Parts Discussed in Thread: LMK05028

Hi,

Let me ask you some questions about DPLL Phase Lock Detectors setting.

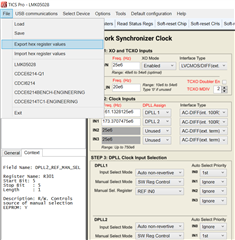

My customer has been evaluating LMK05028EVM with TICS Pro.

The customer would like to make 2 clocks from OUT7 and OUT6 by using IN0 and IN1 input.

But the output becomes following, because "loss-of-phase lock"(LOPC) is detected and then device becomes "HOLDOVER" condition.

IN0 : 161.1328125MHz ---> DPLL1 ---> OUT7 : 173.3707475MHz

IN1 : 173.3707475MHz ---> DPLL2 ---> OUT6 : 161.1328125MHz

The questions are as follows.

Q1) Setting values

The setting values of "DPLL Phase Lock Detectors" are as below.

Are these correct?

If not, please tell me the right one.

DPLL1 : Tph-lock --- 12.93ns Tph-unlk --- 51.73ns

DPLL2 : Tph-lock --- 10.62ns Tph-unlk --- 42.49ns

Q2) If possible, will you tell me how to disable "DPLL Phase Lock Detectors" ?

I attached "setting file" of TICS Pro for your reference.

Thank you for your support.

Best Regards,

Takumicdr_210802_mask3.tcs