Number: CS0695848

Short description: frequency offset issues

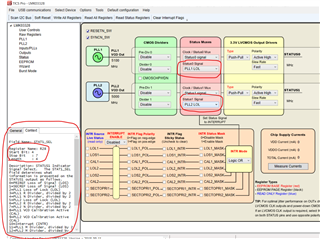

I am using the LMK03328RHST in a design where the LMK03328RHST has both primary and secondary inputs at 10MHz. The LMK03328RHST generates output clocks using PLL1 and PLL2. Using the Status0 and Status1 pins (1 and 2 respectively) to observe the PLL frequencies, I have set the following registers:

R23 STATUS_MUTE to 0x00

R30 PWDN to 0x0A (outputs 2/3 and 5 are powered down while other outputs including CMOSCHPWDN are enabled)

R45 CMOSDIVCTL to 0x54 (PLL2CMOSPREDIV = 01b (4), PLL1CMOSPREDIV = 01b (4), STATUS1MUX = 01b, STATUS0MUX= 00b)

R46 CMOSDIV0 to 0x0B (11 which maps to a divider setting of 12 for PLL1)

R47 CMOSDIV1 to 0x09 (9 which maps to a divider setting of 10 for PLL2)

PLL1 is configured for 4800MHz, divide by 4 on the pre divider and divide by 12 on the divider results in an output clock of 100MHz on STATUS0 output

PLL2 is configured for 5000MHz, divide by 4 on the pre divider and divide by 10 on the divider results in an output clock of 125MHz on STATUS1 output

roughly half the time the circuit is powered on, the expected frequencies are observed on the STATUS0 and STATUS1 outputs. However the other times on power up, the desired frequency occurs for a short duration of time and then 3.3V is displayed on the STAUTS0 and STATUS1 outputs. The outputs, OUT0, OUT4, OUT6, and OUT7 are off in programmed frequency by roughly 5% when STATUS0 and STATUS1 outputs are 3.3V. OUT1, OUT2, OUT3, and OUT5 are disabled through register settings and have no output as desired. For example an output frequency normally measured at 100MHz on OUT6 is measured at 96.4MHZ with an oscilloscope when STATUS0 and STATUS1 outputs are 3.3V.

Can you suggest a cause for this behavior or provide additional troubleshooting suggestions?