Other Parts Discussed in Thread: LMX2594,

Hi team

I am using LMX2594 for making one 75000MHz Clock(RFOUTA) for DAC and one 156.25MHz clock(RFOUTB) for FPGA JESD204B IP Core。I test the clock on LMX2594EVM first

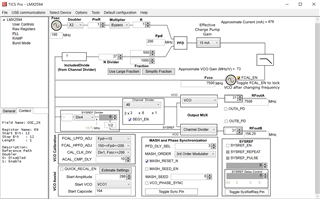

The TICS Pro set is as follows:

Very simple,no using sync and SYSREF functions. but the actually 156.25Mhz output clock has very large spur. and the time domain scope image is not like a clock signal。

But the PLL set didn't violate rules in datasheet. I want to have some debug advise