Other Parts Discussed in Thread: LMX2592, LMX2594

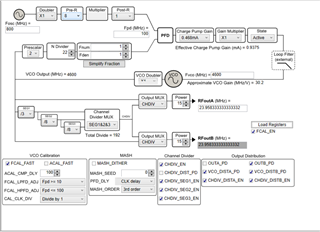

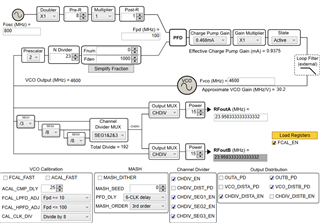

I am evaluating the LMX2592-EVM. It operates well with input frequencies up to about 600 MHz. Beyond that, I am unable to get the board to function. Interestingly, the board will not function with an 800 MHz reference input but if I change the input to 400 MHz and engage the doubler such that the chip sees 800 MHz internally, I get good results. The instructions for the EVM board say to apply 100 MHz and doesn't mention going higher than that. The data sheet specifies operation from 5 MHz to 1400 MHz for the chip itself. Is there a problem with the board that is crippling high frequency inputs?