Hi,

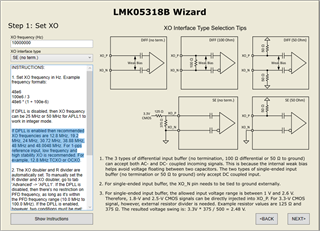

I am reviewing LMK05318B for my design. I tried to put the 10MHz OCXO clock into the XO input and to set it to 10MHz using the TICS pro wizard as shown below, but only a specific frequency is recommended for the following instructions.

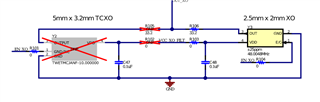

However, I also discovered that EVM made a footprint to use 10MHz TCXO as shown below. Although it is "DNI:...

Question 1. Can I use 10MHz for XO clock? If yes, what are the downsides compared to using the recommended clock?

Question 2. Does the ppm(Frequency stability) of the output clock depend on the crystal (or TCXO) connected to the XO?

I tested with EVM to check phase noise and stability of LKM05318B. When comparing OCXO 10MHz and crystal oscillator on EVM for XO clock, crystal oscillator was better for phase noise, but OCXO 10MHz was better for stability. Please give me some advice on how I can choose the best Stability and Phase Noise.

Thanks.