Hello,

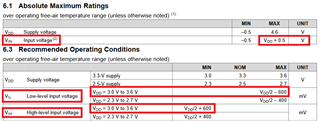

According to the CDCLVC1104 datasheet, when VDD is 3.3V, the input voltage level conditions for the CLCLVC1104 are below.

When VDD is 3.3V, is it correct to input the clock to CLKIN only within the range of VIL and VIH as below?

- VIL = GND ~ 1.05V

- VIH = 2.25V ~ 3.8V

If the CDCLVC1104 user inputs a clock signal with a level out of this range to CLKIN, is there a problem?

Thank you.

JH