Thank you for your explanation.

My question is the maximum capacitor capacity and maximum discharge current.

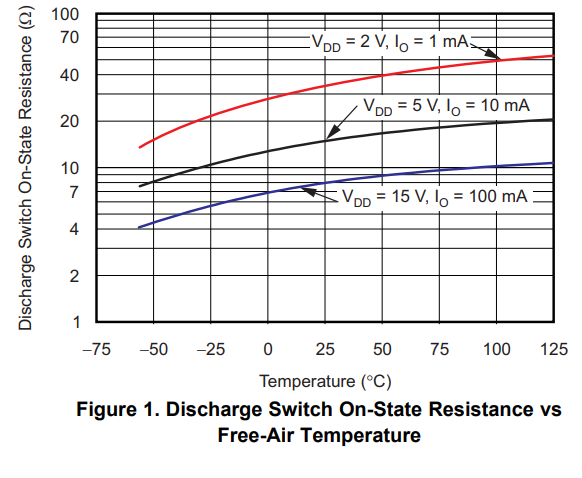

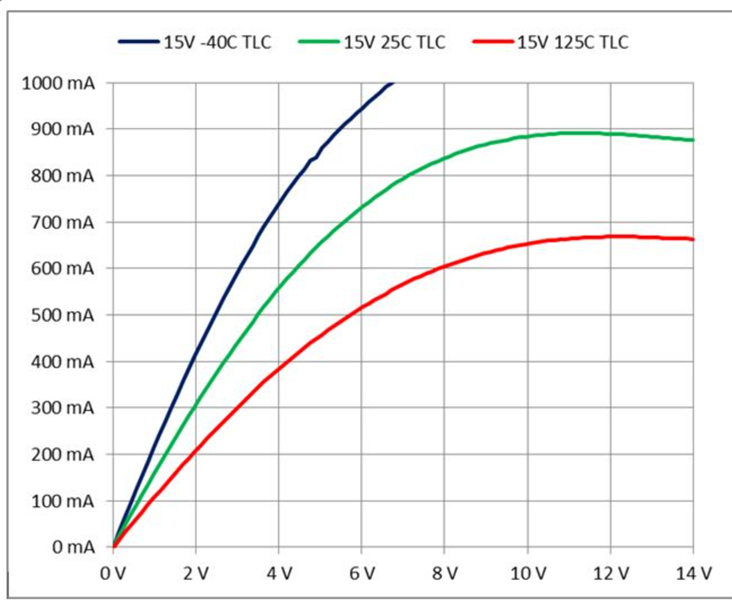

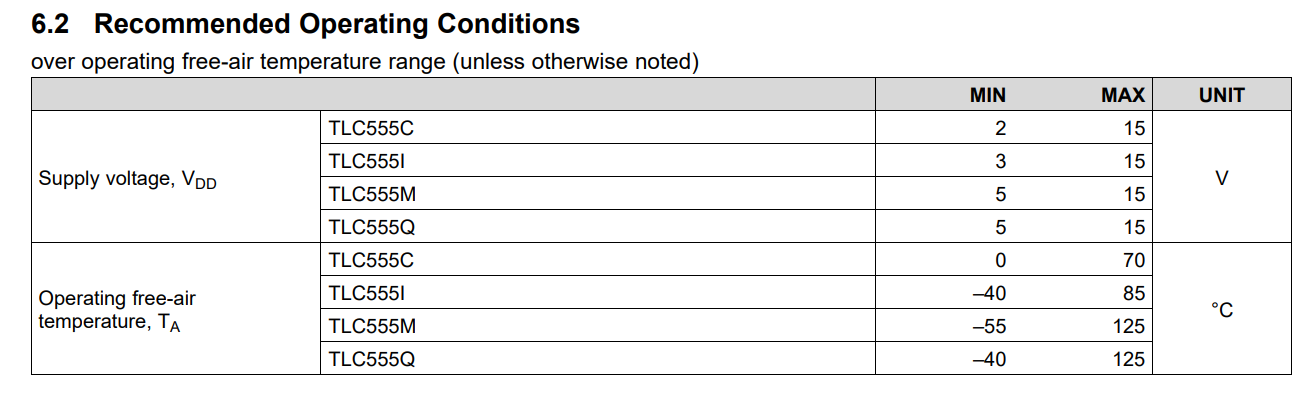

Since it is not specified in the data sheet, I think it will be determined by power consumption and heat calculation.

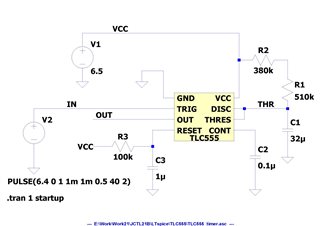

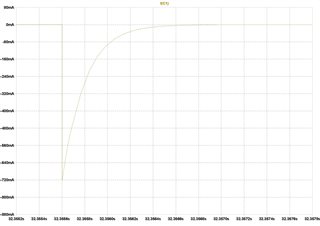

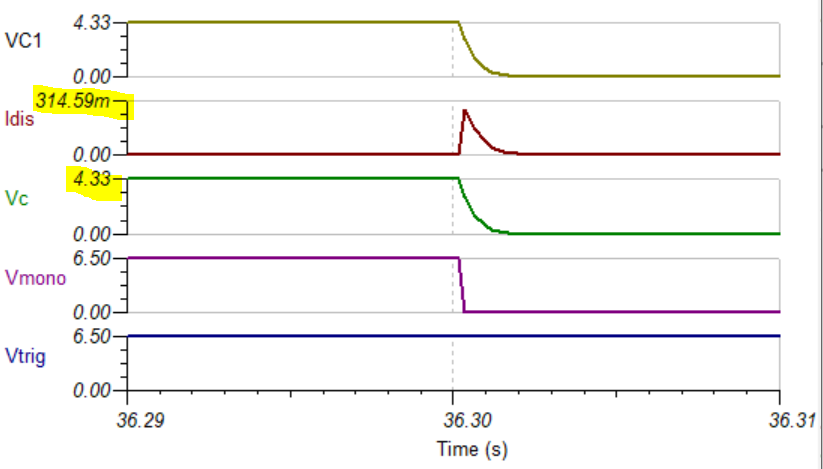

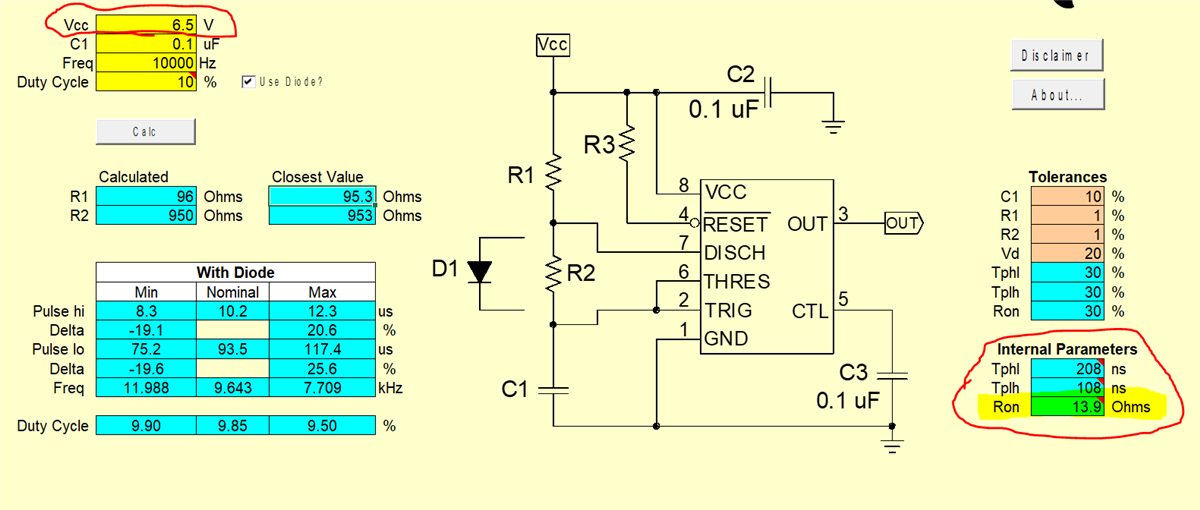

When simulating with LTspice, the peak discharge current from 32uF flows 720mA.

The power consumption is calculated from the current and voltage, and the average power consumption is calculated from the discharge time interval.

Multiply it by thermal resistance to calculate the temperature rise.

I understand that if the temperature is below the junction temperature, it will not break.

Is it correct?

I wonder if 720mA will actually flow in the device.

Is there an internal resistance in the discharge FET inside the IC, and is it limited by the maximum discharge current that can be passed?