Dear Team,

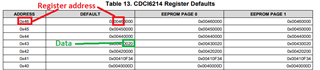

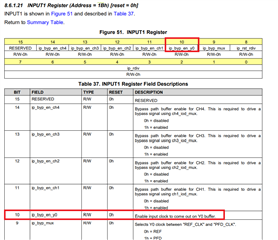

The clock chip CDCI6214 Ultra-Low Power Clock Generator With PCIe Support, Four Programmable Outputs and EEPROM used in the project.

Which register should be written for the initialization of this clock chip? Write what? What does the control timing and logic look like? Can you provide reference logic code or documentation?

Many Thanks,

Jimmy