Other Parts Discussed in Thread: LMK5C33216

Hi Team,

Is there any bit or way to confirm whether the input port of LMK04832 has a clock signal? Thanks.

B.R.

Zhizhao

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Team,

Is there any bit or way to confirm whether the input port of LMK04832 has a clock signal? Thanks.

B.R.

Zhizhao

Hi Zhizhao,

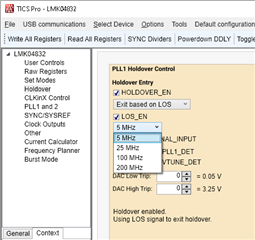

Yes, there is a LOS feature that will allow you to detect the presence of an input clock on CLKin lines.

When AC coupled, set the CLKin to MOS input. This ensures hysteresis between the inputs to prevent random chatter to defeat the LOS circuit.

After enabling the LOS_EN, set the LOS_TIMEOUT frequency to below something below your input frequency.

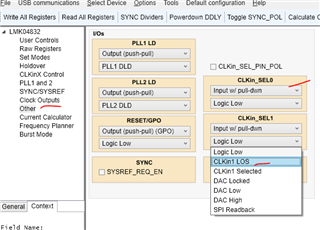

The CLKin_SELx lines can be configured to output CLKinx_LOS.

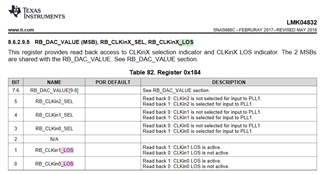

Or you can read back from R0x184:

73,

Timothy

Hi Timothy,

Thanks. I tried the 2nd solution. I readback 0x184 with input and W/o input, but I found this register didn't change. Is there any more configuration I need to do before readback 0x184?

B.R.

Zhizhao

I think I got you point. You means if I want to readback 0x184 register, I need first set CLKin to MOS input, enable LOS_EN, set LOS_TIMEOUT frequency to below input frequency, am I right? But I found the input signal is recovered 1.92MHz clock from CPRI, it is smaller than 5MHz. How could I configure in this case?

Hi Zhizhao,

Ah yes, that is a trouble - 1.92 MHz is < 5 MHz and therefore this LOS detector would always think the signal is invalid.

Unfortunately I am not aware of any workaround for this except to increase above 5 MHz (which is the typical threshold value).

If this functionality is required, please consider one of the DPLL products. These have much more advanced input detection, holdover, and switching features. Consider LMK05C33216 as it can produce frequencies similar to LMK04832. On LMK5C33216 APLL2 can be used for 2949.12 MHz type frequencies (but does not have the frequency range for 3200 MHz) and LMK5C33216 APLL3 is the BAW which provides very low phase noise for 2457.6 MHz type frequencies.

73,

Timothy

Hi Timothy,

Thanks! Got that. May I know what is the principal of detect the input signal? Does it detect the input clock rising edge and count?

B.R.

Zhizhao

Hi Zhizhao,

LOS in LMK04832 is a time constant which gets reset by clock input edges... so if there is no new clock input edge, it times out and LOS is asserted.

73,

Timothy