Hi team,

Another customers' question.

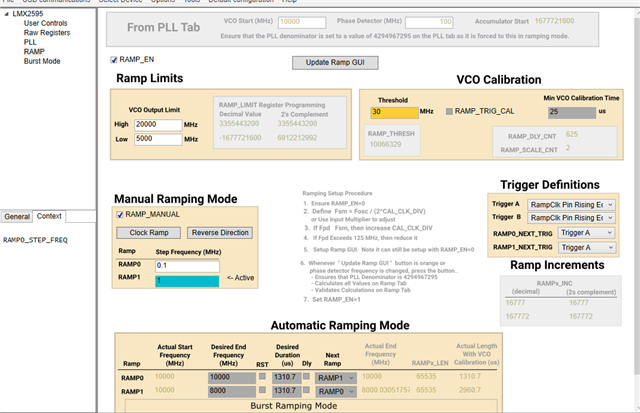

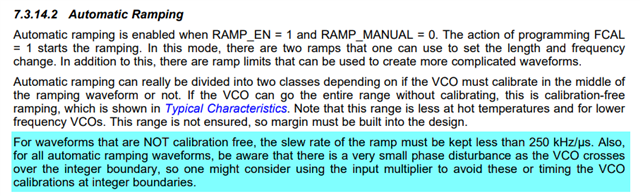

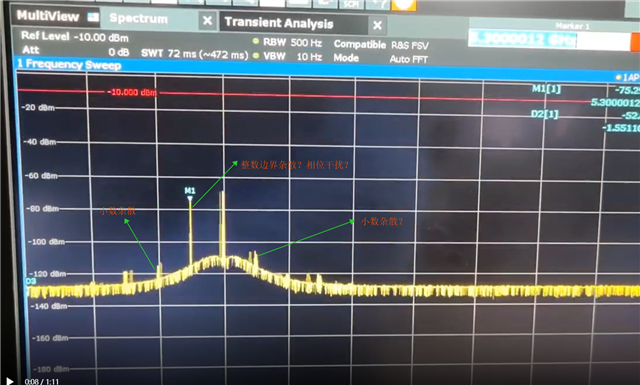

For manual ramp, is the clutter at an integer multiple FPD frequency a phase interference, (integer boundary clutter)? Does this have an effect on the continuity phase? Here the clutter is one occurring at an integer multiple FPD and one symmetrically on the other side of the main signal, as shown in the figure:

Is there a way to avoid or eliminate this clutter of integer boundaries? Does TI have quantitative data on the effect of the initial mash order on this integer boundary in ramp mode?

Best Regards,

Amy Luo