Other Parts Discussed in Thread: AFE7950, LMK04832, AFE7950EVM, LMK04828

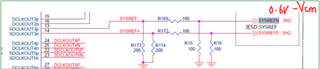

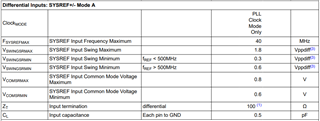

Hello TI e2e, I was hoping to get some design recommendations for a design involving the TI LMK04832 and AFE7950 parts. The design involves generating a 3.90625 MHz LVDS clock from the LMK, which feed into the SYSREF inputs on the AFE. I would be using one of the odd CLKOUTX pairs on the LMK. My question involves LVDS common mode biasing, because according to your AFE79XX_schematic_layout_checklist on the secure site, the SYSREF needs to be set externally to 0.6 V, which is the min Vcm on the AFE datasheet, pg 19 (snippet below) and the max Vcm being 0.8 V. The typically VOD swing is 0.75 Vpp.

I was provisioning for 0.1 uF AC coupling on each SYSREF +/- line, which would remove DC offsets and alter the common mode voltage level, but this may not be optimal for what the AFE SYSREF input is expecting, and I'm sure about the its biasing capabilities. Could any suggestions be offered for setting the common mode externally? Perhaps I would need a resistor network to DC return current paths? Thanks for your time.