Other Parts Discussed in Thread: LMK5C33216, LMK5B33216, LMK05028, LMK5B12204, LMK04033, LMK04000, LMK04001, LMK04011, LMK04010, LMK04002, LMK04031, LMK04610, CDCE813-Q1

Hi team:

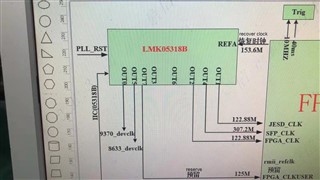

I would like to confirm whether we have a low consumption device as <1W to substitute the LMK05318B.

tks for you confirmation.