Hello,

My customer is using the LMK03806 with the following setting.

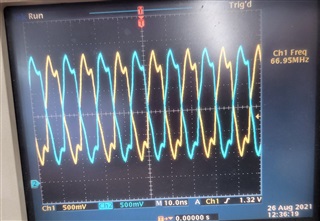

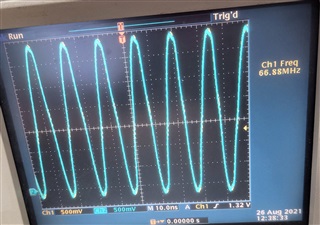

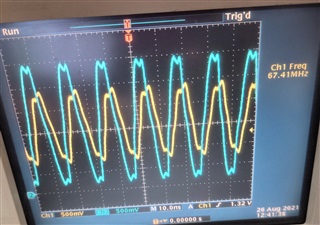

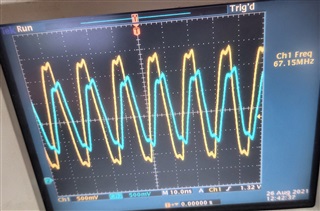

The capture image of the LVCMOS (Norm/Low) output is as follows(Yellow=P port/ Blue=N port).

They thought the N port output would be Low, but there is clock output.

Please help us with the cause of this problem and how to fix it.

Thank you.

JH