Hello

I designed LMK04803 board, and the registers generated byTICS Pro. PLL2 is not locked.

Input clock frequency: 40MHz,COMS;

Output clock frequency:80MHz, LVDS, x10;

Mode:PLl2,Int VCO, 0-Delay。

The HEX-file generated by TICS Pro:

R0 (INIT) 0x80160100 R0 0x00140300 R1 0x00140301 R2 0x00140302 R3 0x00140303 R4 0x00140304 R5 0x10140305 R6 0x11110006 R7 0x11110007 R8 0x0611B808 R9 0x55555549 R10 0x9142590A R11 0x41F0100B R12 0x130C006C R13 0x3B02800D R14 0x0200000E R15 0x8000800F R16 0xC1550410 R24 0xAC000058 R25 0x02C9C419 R26 0xAFA8001A R27 0x1000009B R28 0x0010009C R29 0x0080031D R30 0x040000DE R31 0x001F001F

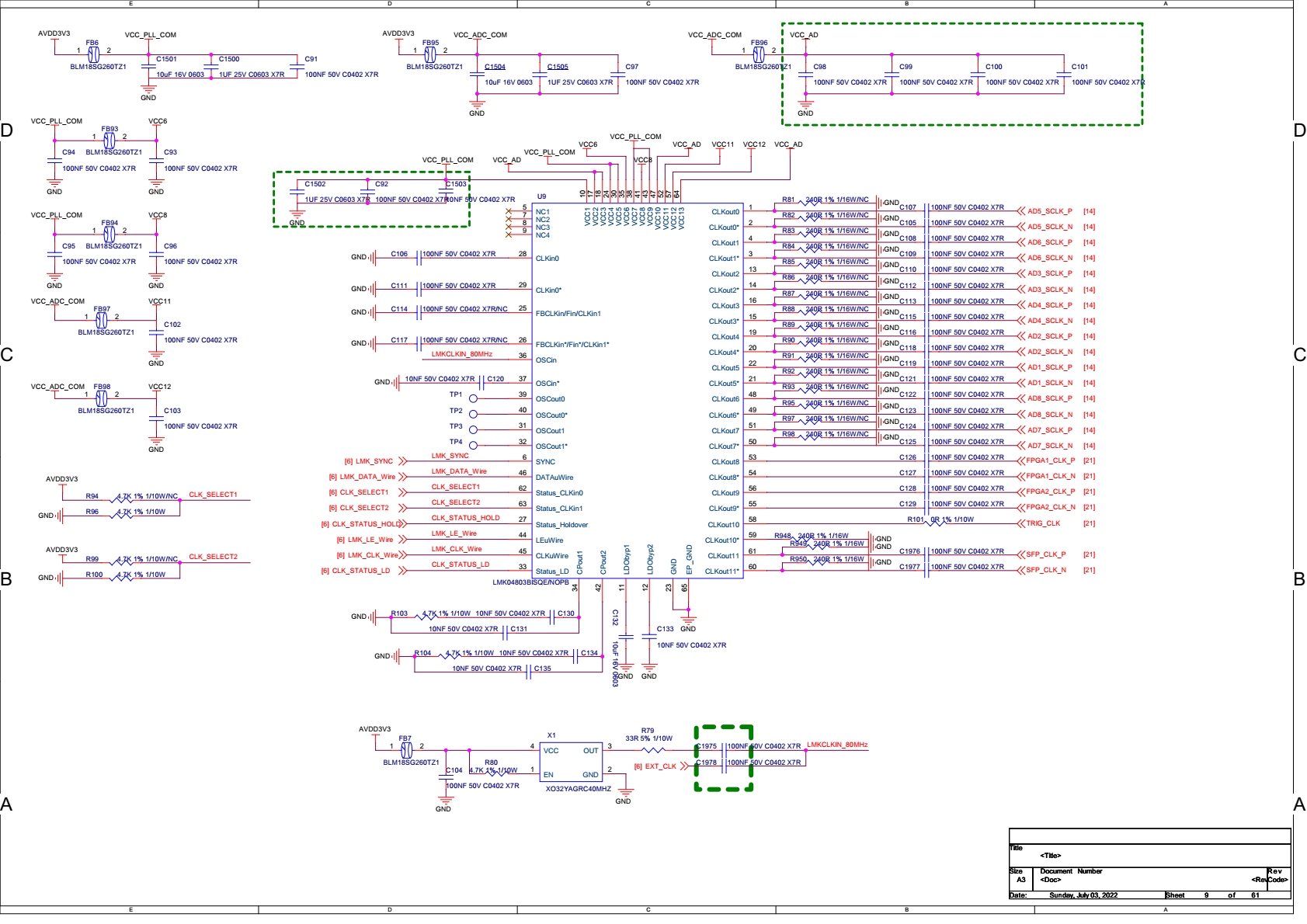

The Schematic:

The noise of the VCC_PLL_COM is 30~40mVpp.The regisisters readbacked was normal.

Thank you.