Other Parts Discussed in Thread: LMK05318, , CDCE6214

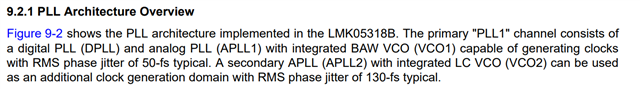

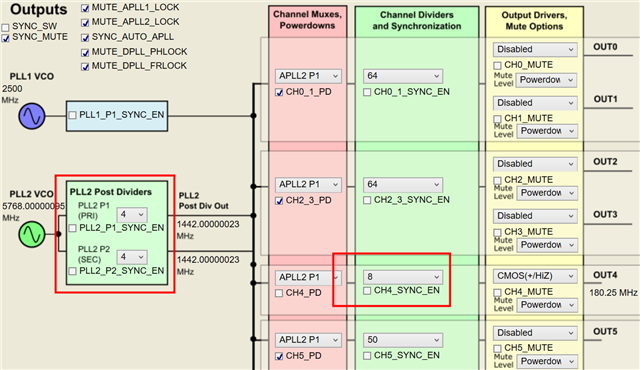

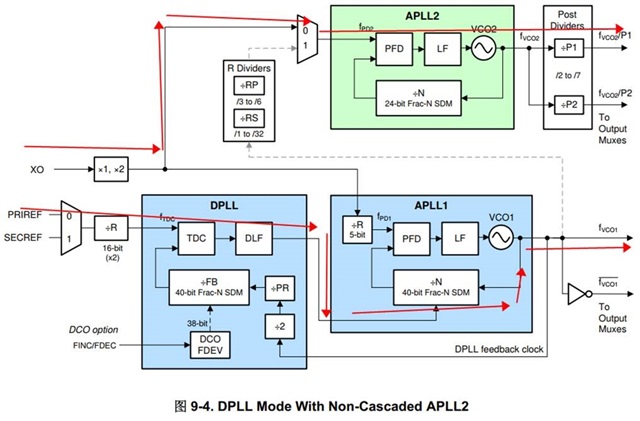

Hi, I have some question for LMK05318 as below:

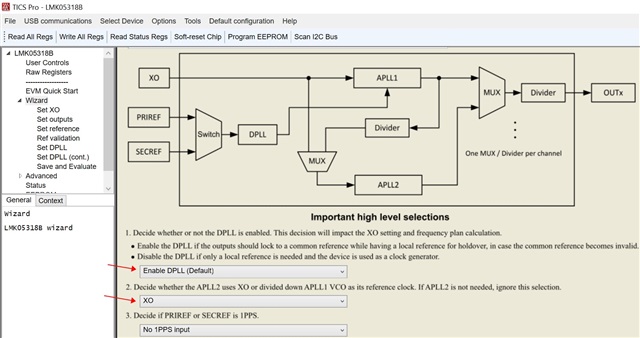

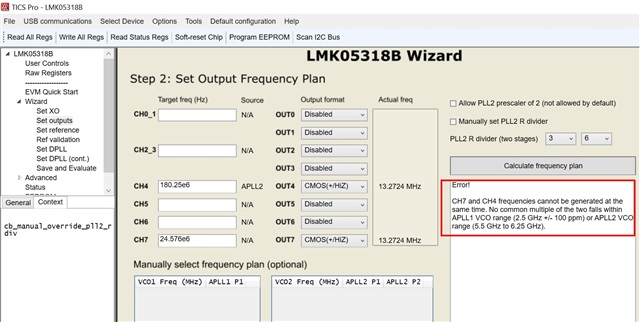

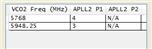

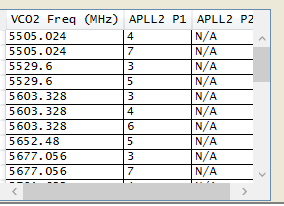

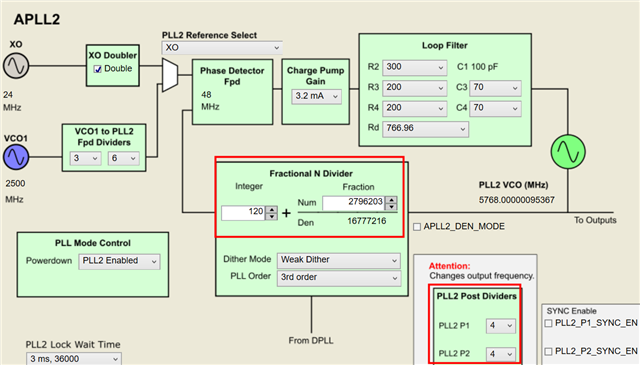

1. Can the 180.25Mhz used for 15" screen refer to XO output as shown below, and the 24.576Mhz used for audio refer to PRIREF output? It feels like there is no conflict between the two clock path,

2. Can it output 180.25MHz and 24.576MHz at the same time? If so, how can it be configured?