Hello,

we are trying to generate a 500 MHz signal with the LMK04808 Dual-Loop configuration. However, we are not able to get the PLL1 to lock (PLL2 is locking).

The reference input (CLKin1) is a 125 MHz clock signal. The VCO we are using is this 200 MHz VCXO from Abracon: https://www.mouser.de/datasheet/2/3/ASG-P-35446.pdf

PLL1 PD parameters:

- Frequency: 25 MHz

- Gain: 100 uA

- Positive Polarity

PLL1 loop filter values:

- C1: 39 nF

- C2: 1.8 uF

- R2: 2.2 kOhm

For full configuration of the device please see the hex register values from TICS Pro: /cfs-file/__key/communityserver-discussions-components-files/48/Dual_5F00_Loop_5F00_config.txt

We checked the PLL1 R and N divider output frequencies, which seem to be ok.

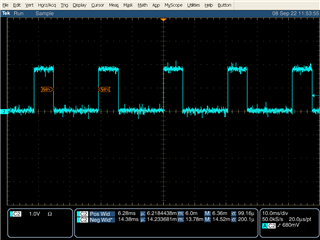

However the PLL1 DLD signal looks like this:

We tried to play with the PD parameters, but this did not visibly affect the behavior.

From our understanding the configuration should be working. Maybe we still missed something?

Otherwise we suspect that the VCXO chosen might not be suitable for this device.

Could you help us with this issue or indicate where the problem could possibly be? Please let us know if more information is needed.

Thank you in advance and best regards!

Olena