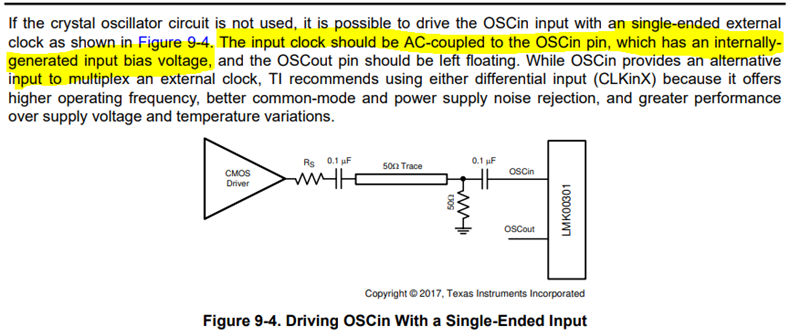

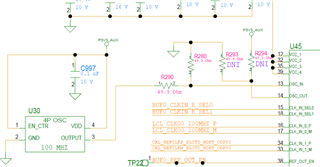

1- Would I be damaging OSCin inside buffer by applying a CMOS OSCILLATOR output directly to OSCin pin? The OSC's 3.3V CMOS output is divided by 2 via 2 x 49.9 ohms and fed to pin 13 (OSCin). no AC coupling cap is implemented.

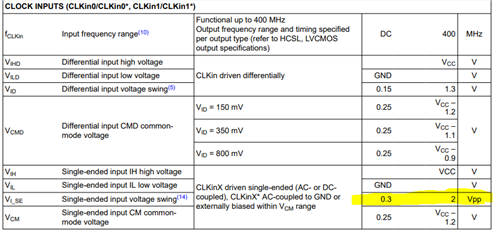

2- Am I over driving the CLK_IN_X_P/N by feeding these inputs with a greater than 1.3V swing clock signal? I am not getting anything at the outputs, so I thought may be I should bring the input amplitude down.

Thanks,

Bahram