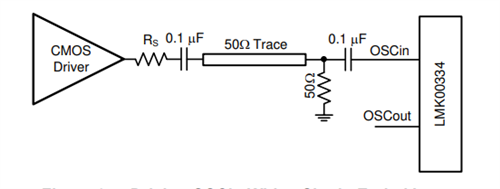

Other Parts Discussed in Thread: LMK00334

I have problem with LMK00338 8-Output PCIe clock buffer. The outputs are "dying" with time for unknown reason.

For instance, the swing of the positive or negative leg of some outputs could become about a half of a full swing. Some outputs are just not responsive (dead).

Also, after some time (10 minutes) all output could become unconscious (happen sometimes). They will be recovered after a short power down break.