Other Parts Discussed in Thread: CDCE913

Hi Expert,

I have CDCE913 IC, configure through i2C.

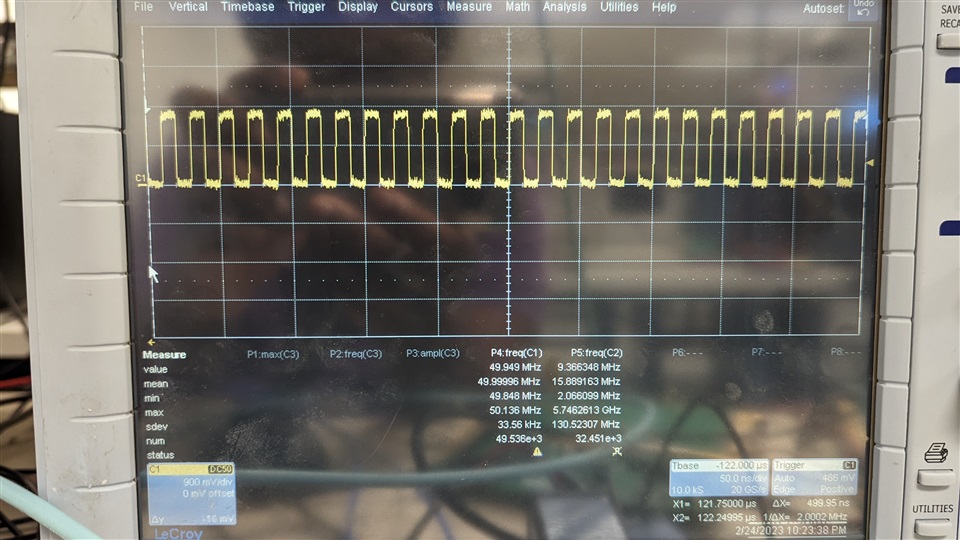

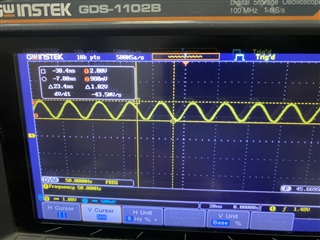

I am able to get desired output frequency but my amplitude and pick to pick voltage is changing when i am changing the frequency. Is it like that only or something is wrong. PFA image for reference.

- Default 25MHz frequency

- 50Mhz frequency with the following setting

- M=4

- N==40

- Fin=25Mhz

- Fvc0=250Mhz

- Pdiv=5

- P=1

- Q=20

- R=0

- configuration register is

- output selection Y1_7,FS1_7,SSC1_7 and Y2Y3_7

- Y1_ST1 = 01, Y1_ST0 = 11

- XCSEL = 0x09

- SSC1_7 = 0b0111 / 0b001

- Y2Y3_ST1=01, Y2Y3_ST0=11

- SSC1DC = 0/1

- VCO1_0_RANGE = 11 >175MHz

- VCO1_1_RANGE = 11 >175MHz

Please help me out.

Waiting for your feedback.

--

Thanks & Regards,

Divyesh Patel