|

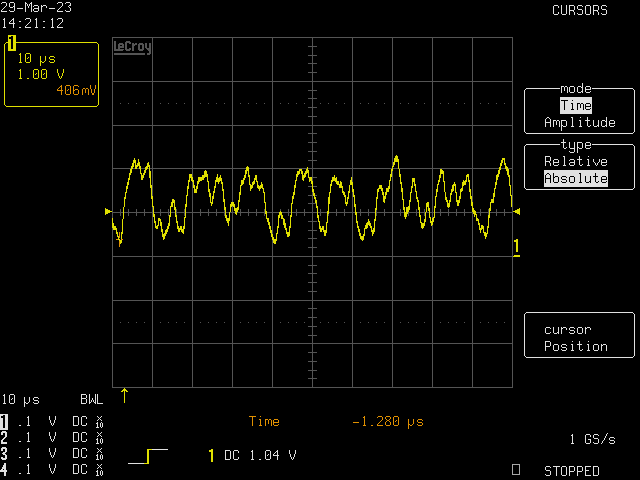

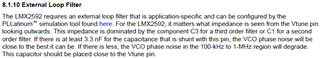

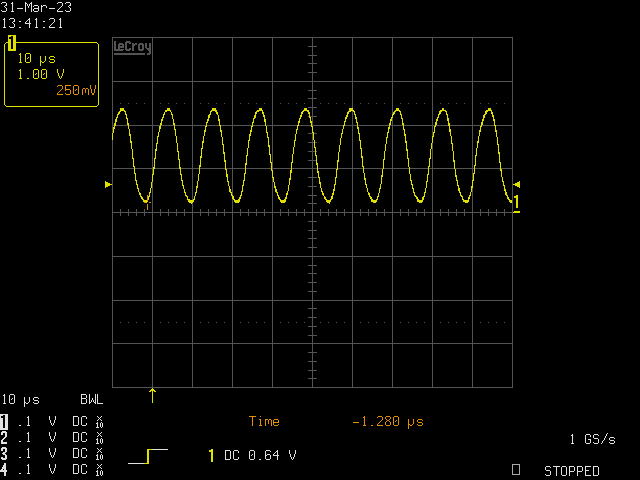

Dear Sirs, I am having trouble getting stable PLL operation using the LMX2592. The following are the parameters: reference frequency: 10MHz Phase detector frequency: 20MHz VCO frequency: 6.834682GHz Integer divider: 170 Fractional modulus: 4000000000 Fractional numerator: 3468200000 I have programmed the registers to the Aug 2022 revision. The output is centered around the correct frequency, however shows FM with a peak deviation of 40MHz. Looking at the tuning voltage on pin 35, a near sine wave is seen with a frequency of 87kHz, and an excursion from 0.2V to 2.3V. The auto calibration is obviously working as the VCO is centered on the correct frequency. I have taken the loop filter values from the Platinum Sim program, and the design is attached. I have checked the loop filter components. I have tried different charge pump currents with no or little change. I have tried setting the PFD_DLY parameter to 32 ( not used). This has a large effect on the tuning voltage. The sine wave is replaced by random noise. (Attached) I have carefully checked the register readback for incorrect values, but may have missed something. Please check the register dump for incorrect values regards Cosmo Little (RF Solutions)

|

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.