Hello,

Our customer used two CDCE62005 for cascade application. But some of the board the second CDCE62005 couldn't be lock.

His description is as following:

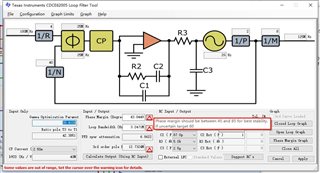

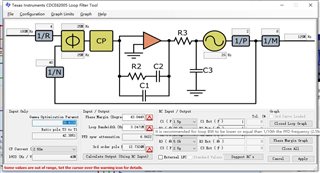

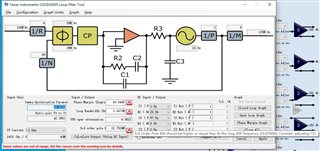

Our circuit is fully referenced to TI's official 6678 development board, configured with an SPI interface controlled by an FPGA, and configuration files generated by official software;

We has produced too many batch cards, but from last year began to fail, last year accumulated 2 cases, this year so far 7 more cases!

The failure to lock occurs only in the second stage; the failure to lock occurs in the second stage by reversing the front and rear chips of a faulty board.

The swap experiment eliminated the chip problem, non-new board eliminated hardware problems and software problems, the swap experiment and non-batch board card problems solved the welding problem, the next troubleshooting method is not clear.

Please tell us about the possible cause of the problem and its resolution.

Best regards

kailyn