Tool/software:

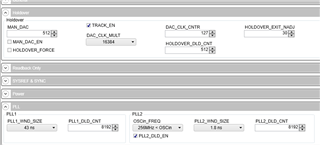

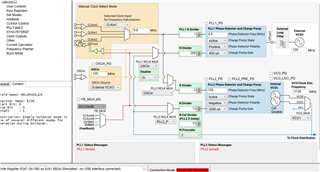

To determine if the PLL is locked, I made the following settings:

I want to observe the lock status of PLL1 and PLL2 through Status_LD1 and Status_LD2.

The configuration of PLL is as follows, using two PLLs at the same time and using a 120mHz VCXO externally:

Real machine testing has found that Status LD2 is high and Status LD1 is low.

When the external input clock source (600kHz) is turned off, there is no change in the status of Status LD2 and Status LD1.

As expected, when there is a clock input, Status LD2 and Status LD1 should be raised to indicate that PLL1 and PLL2 are locked. When there is no clock input, Status LD2 and Status LD1 should be low.

But that's not the case. May I ask where my configuration is problematic?

Also, I would like to ask if it is possible to use Status LD2 or Status LD1 to observe whether it is locked using only one PLL?