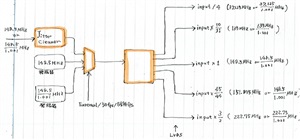

Please let me know recommended clock solution.

(Attached below)

※Jitter cleaner input are LVDS or LVPECL.

Clock generator output is LVDS.

・I think that jitter cleaner is CDCM7005, but Clock generator and Switch were not find best solution.

Best regards,

Satoshi