Other Parts Discussed in Thread: LMX2581, CODELOADER

Dear Specialists,

My customer is testing LMX2581EVM.

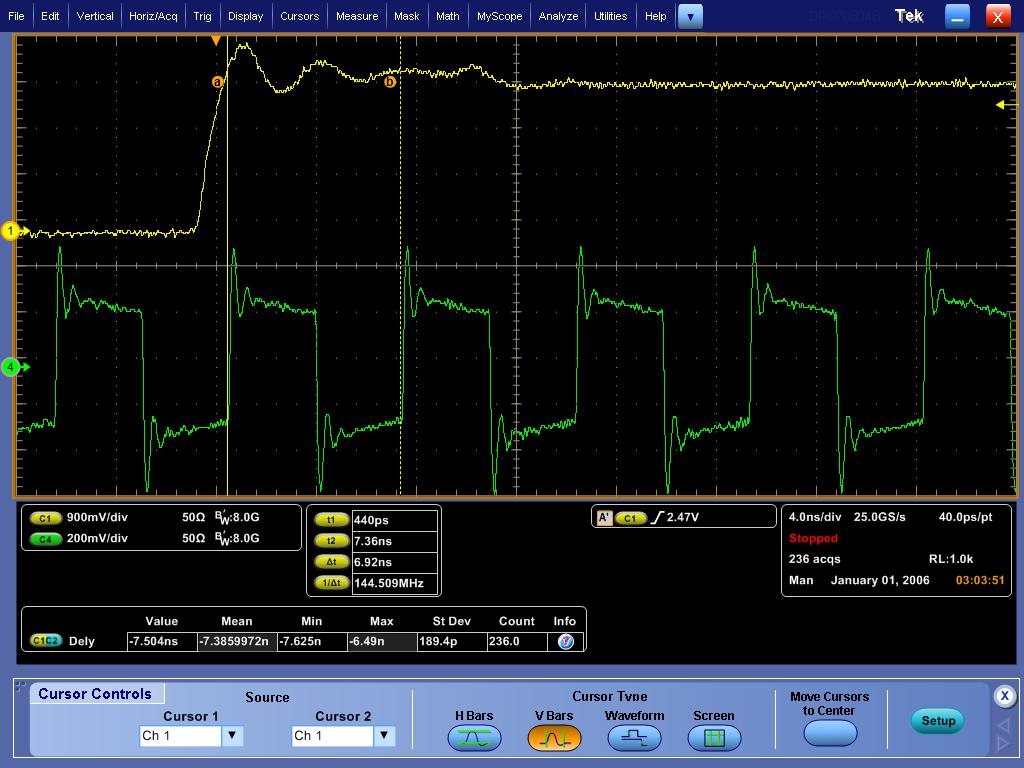

He confirmed phase shifts between input reference and output.

The phase shift is not constant value, different value at the moment to moment.

Could you please see three attached files.

(1) is this phenomenon normal, or not?

(2)If so, how much is the maximum phase shift?

(3)Why does the phase shift happen?

He wants to design a perfect synchronous timing circuit, he has to know how much is phase shift in detail.

I appreciate great help.

Best regards,

Shinichi