Good day! I have a problem with LMK03033 configuration. I used the following registers (verilog):

32'h80000000,

32'h00030300,

32'h00030301,

32'h00030302,

32'h00030303,

32'h00030304,

32'h00030305,

32'h00030306,

32'ha0032a09,

32'h0082800B,

32'h28E000D,

32'h1840020E,

32'hCC00180F

At the output of the device, I see 105 MGh and Lock Detect is't working, when at the input is 56 MGh.

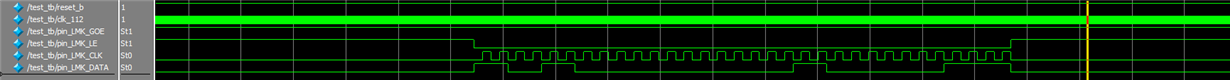

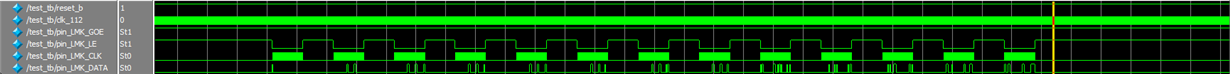

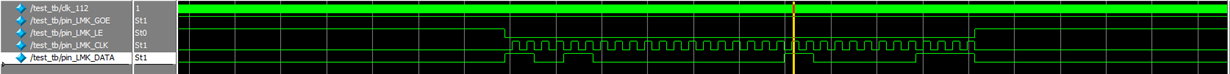

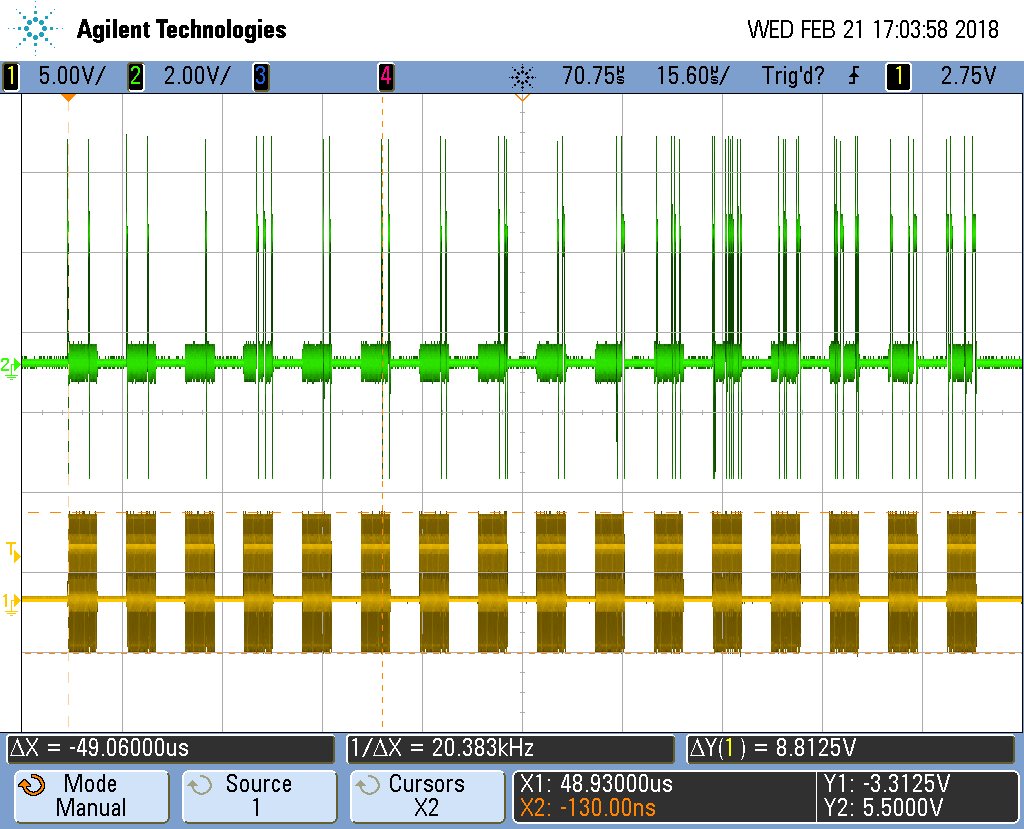

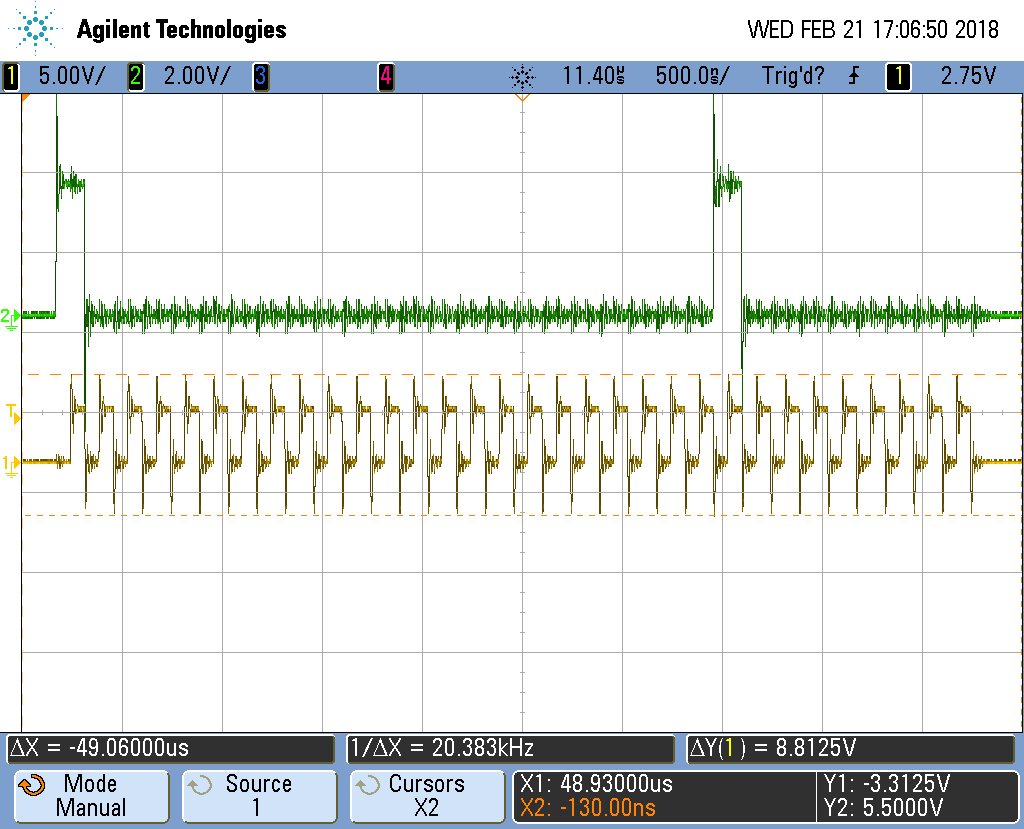

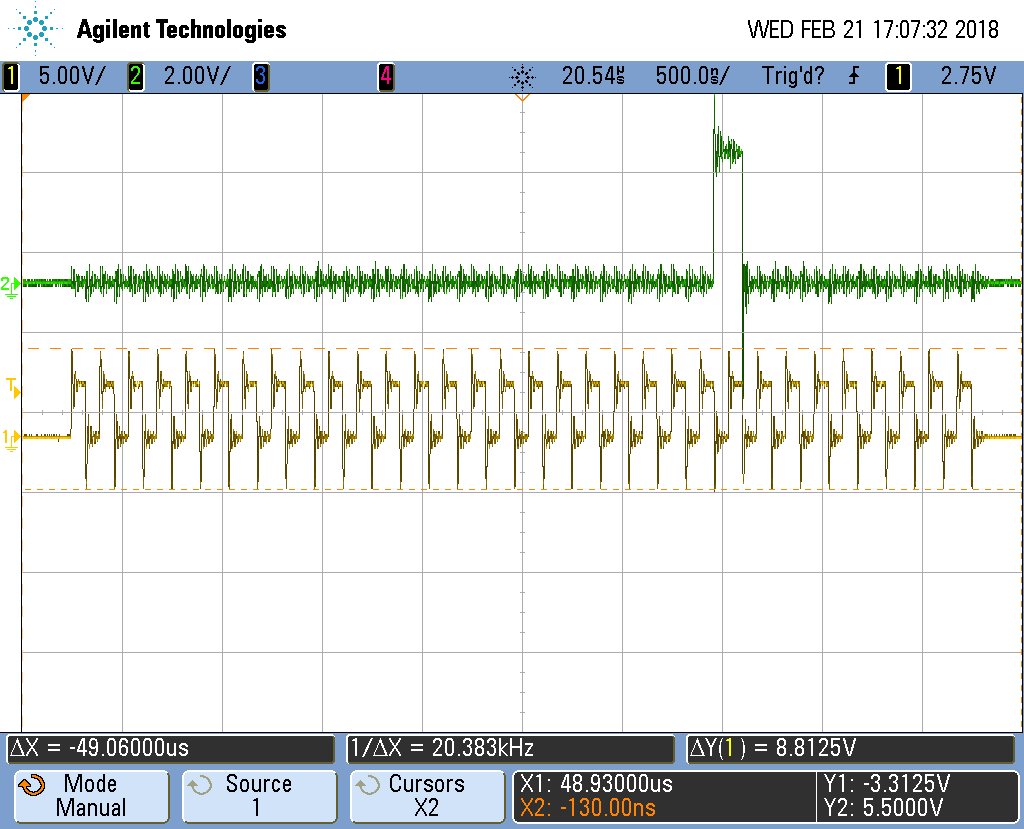

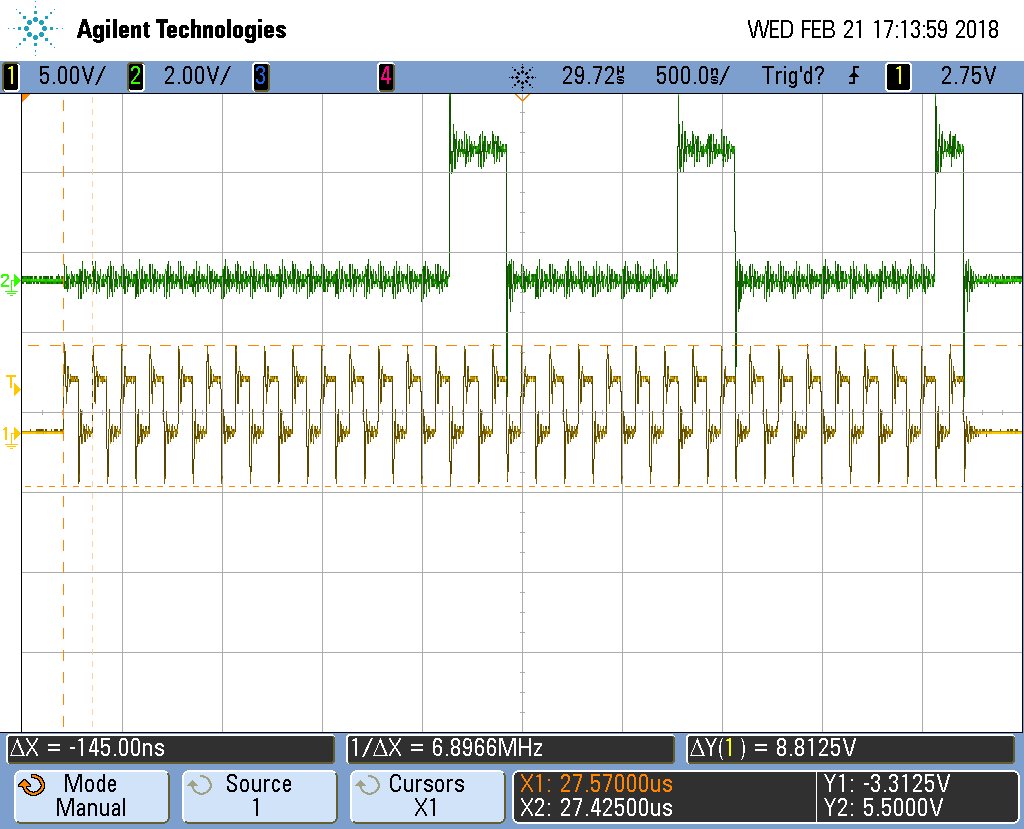

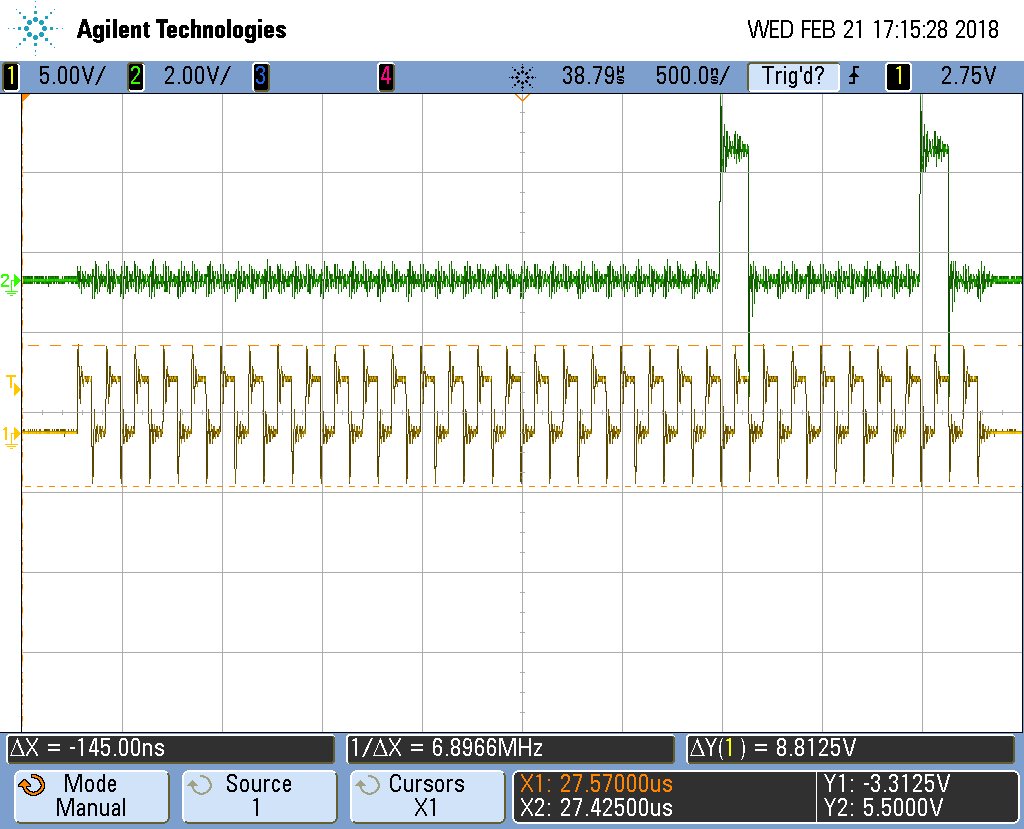

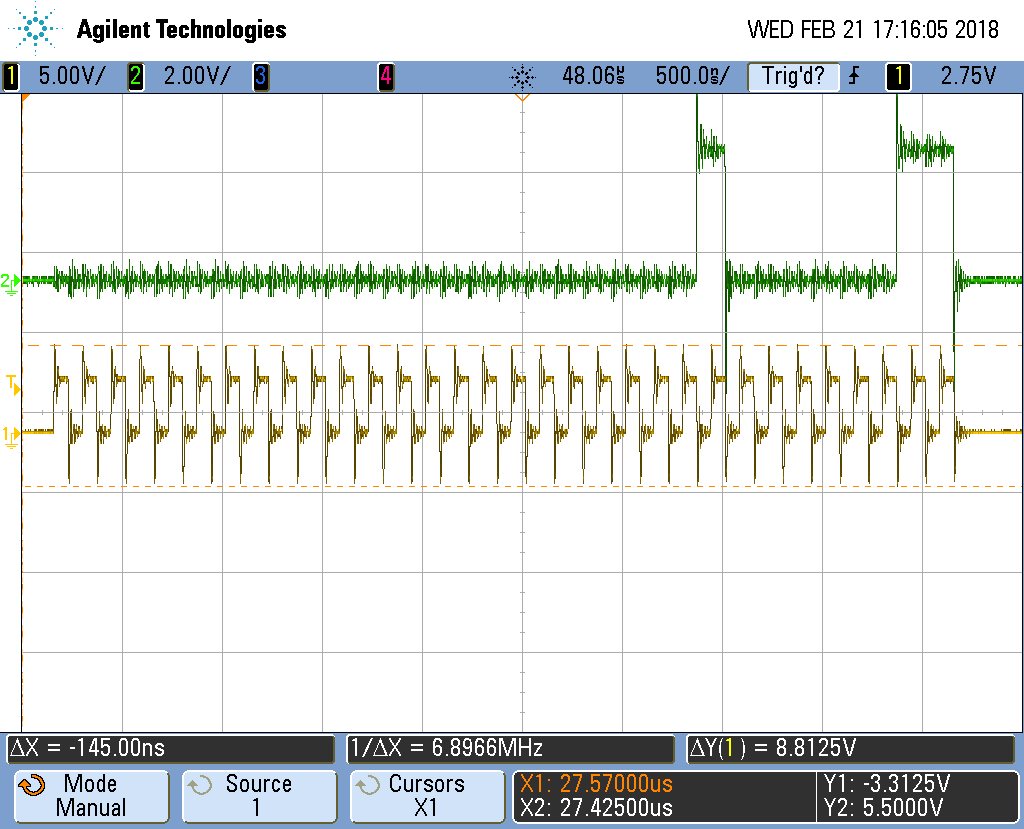

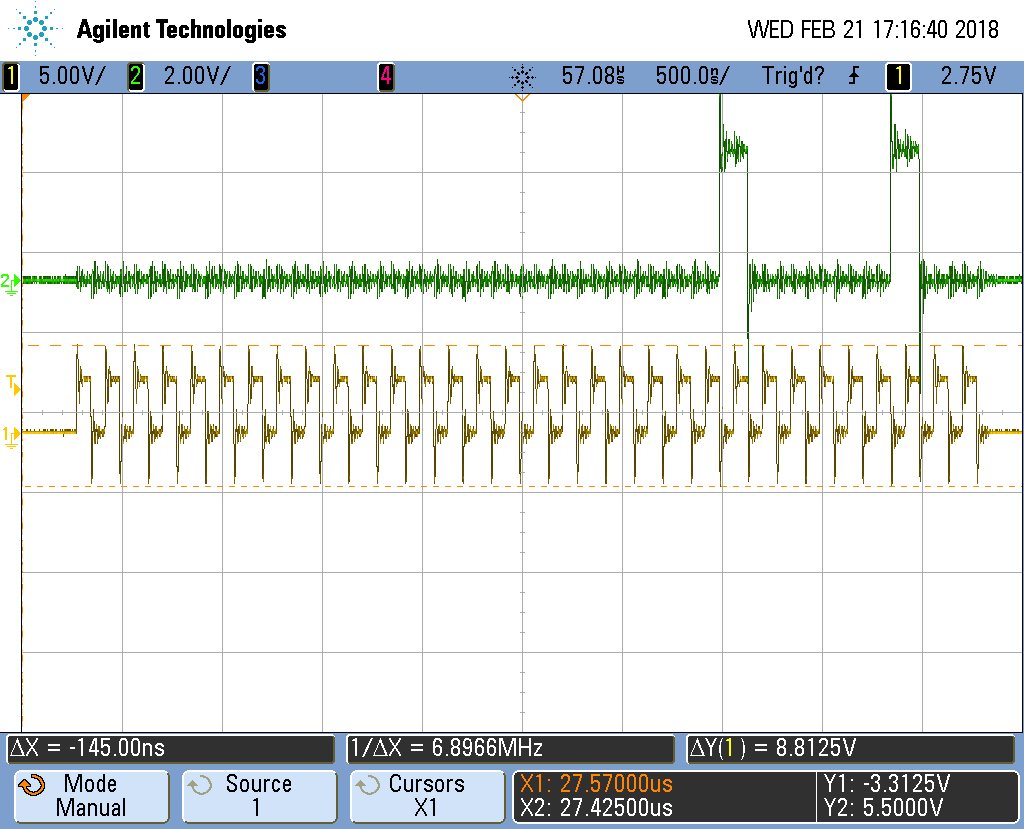

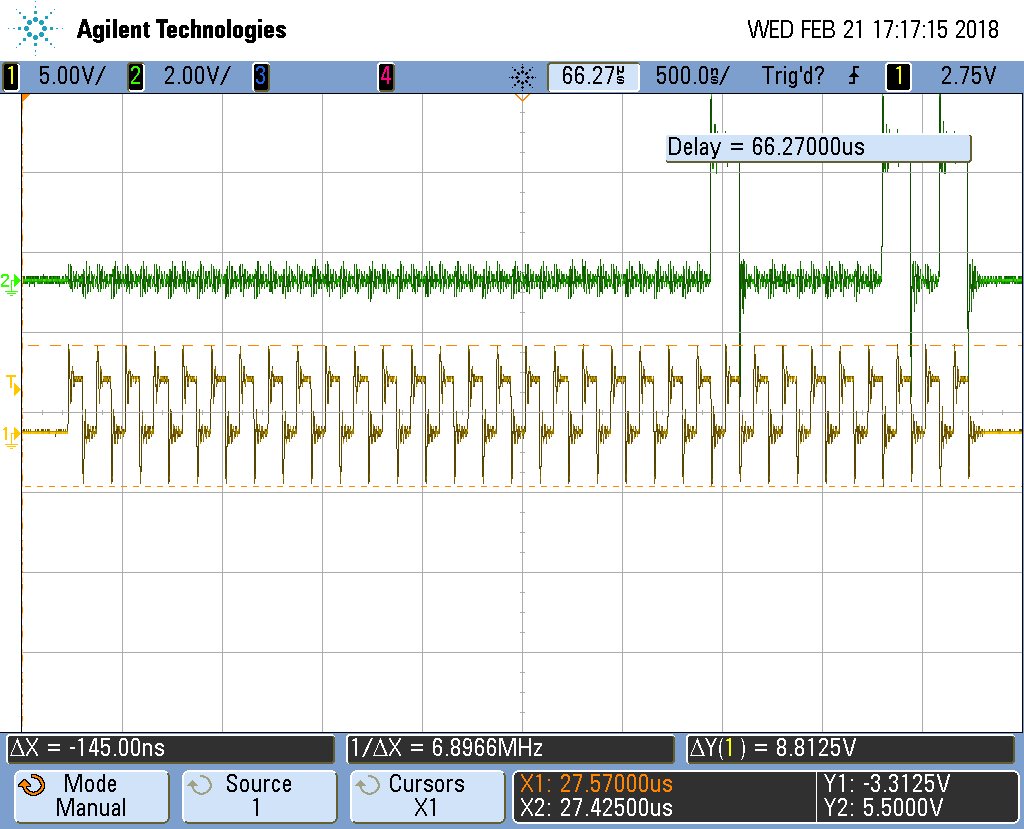

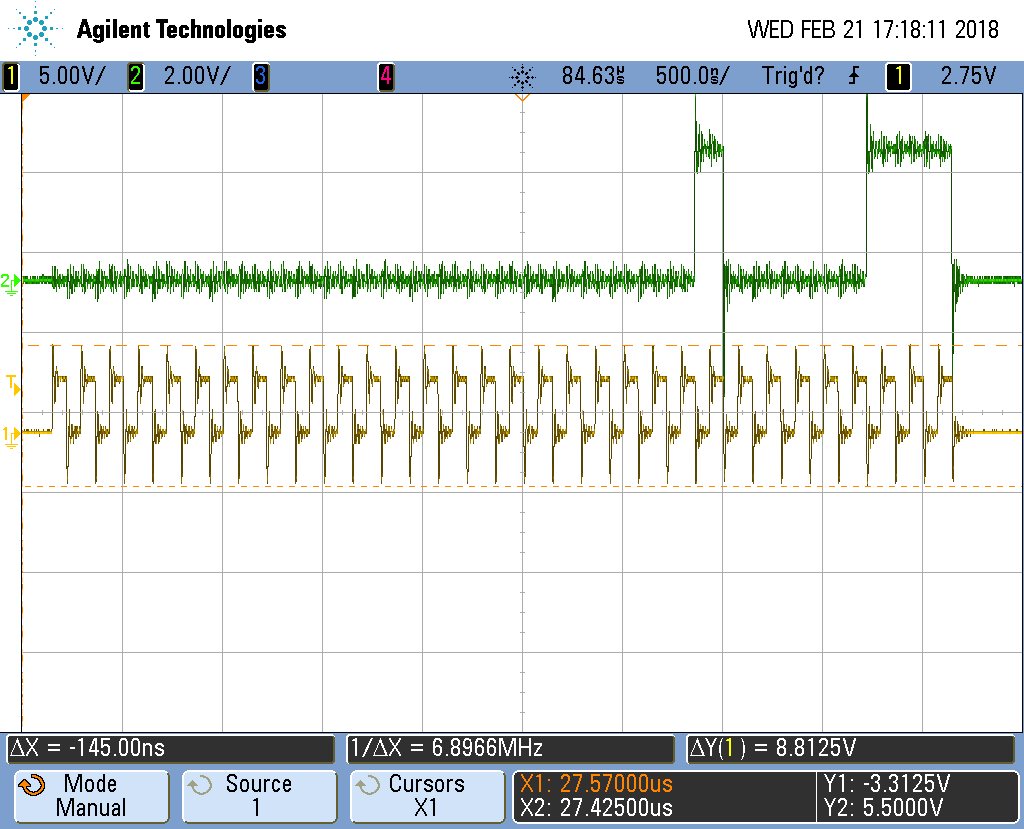

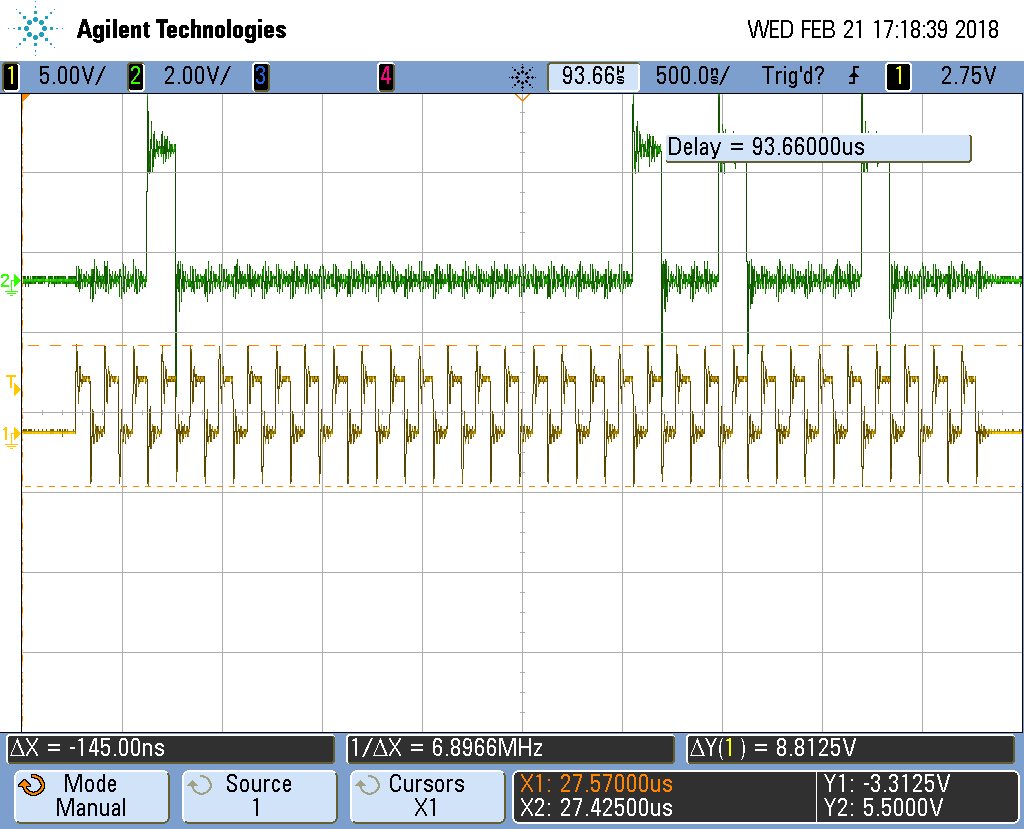

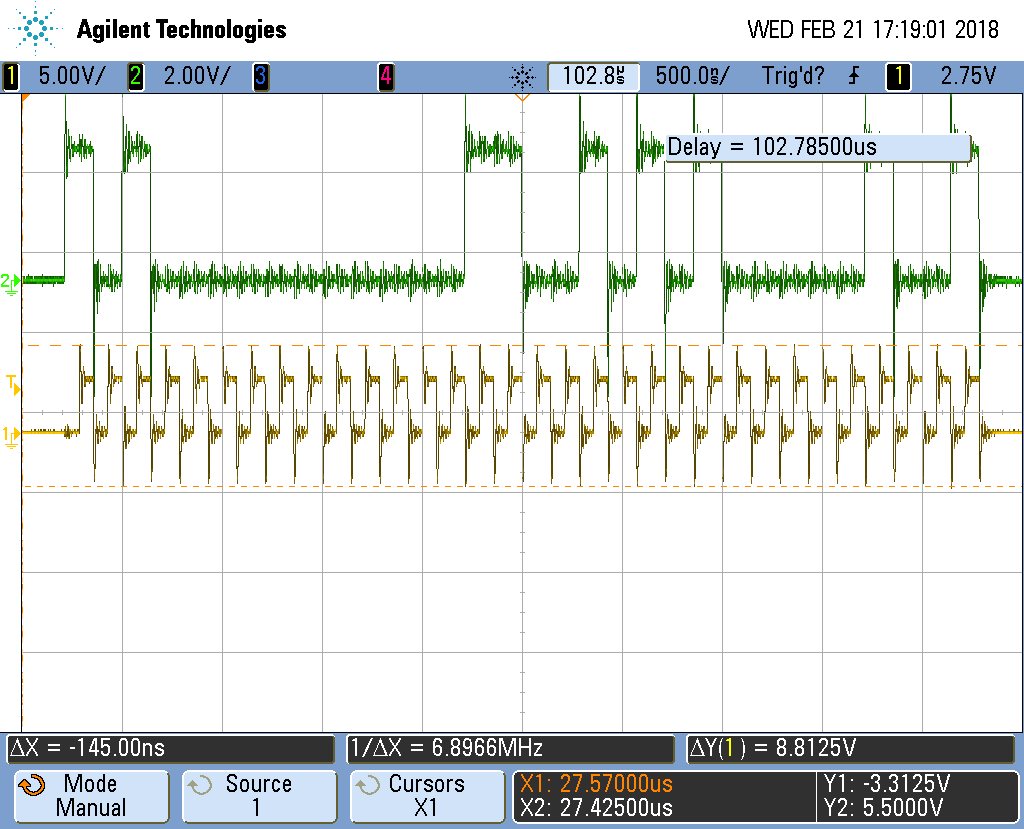

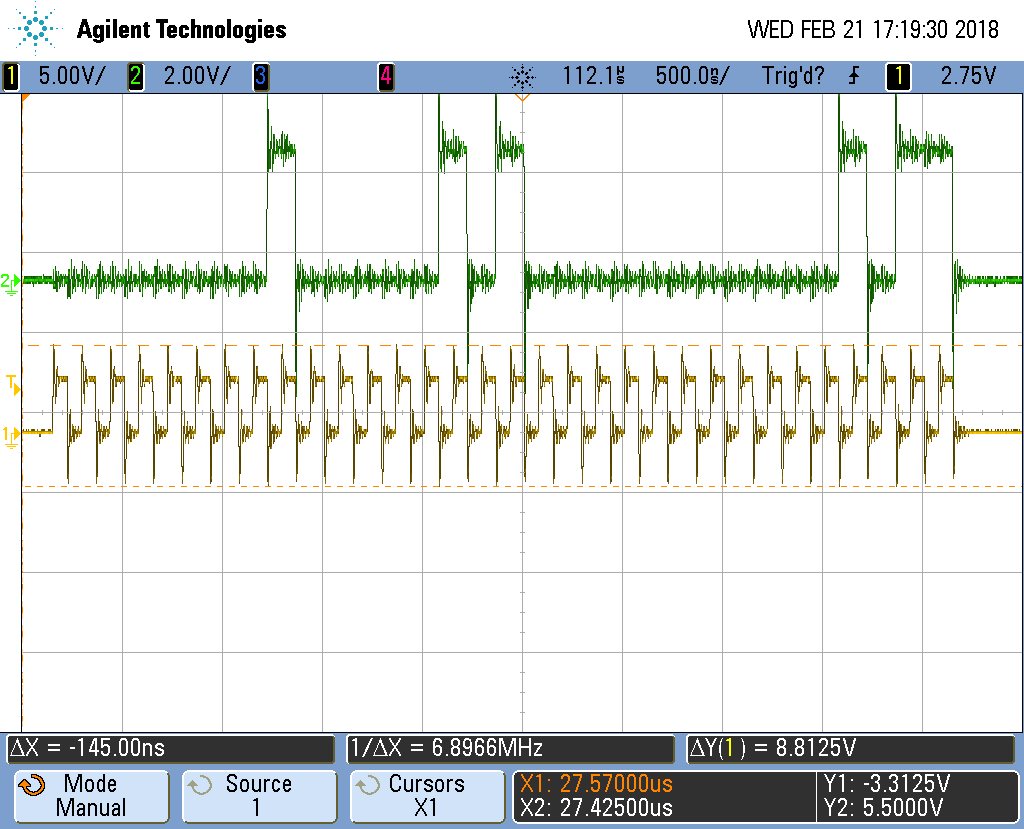

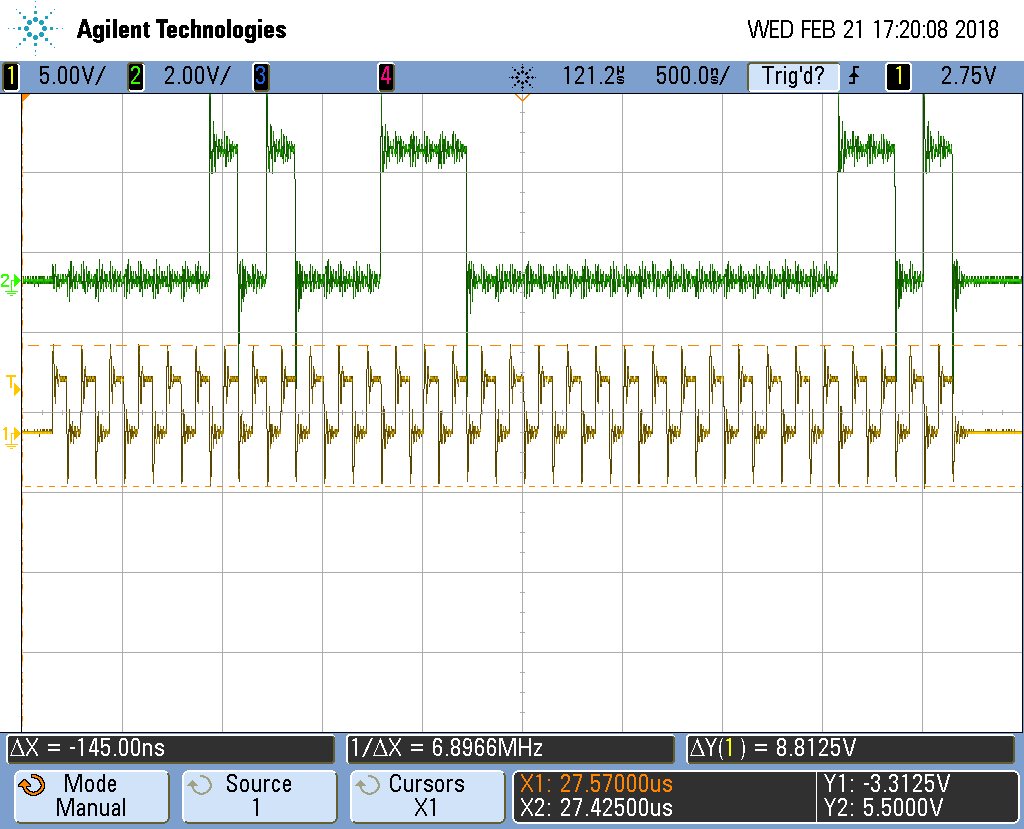

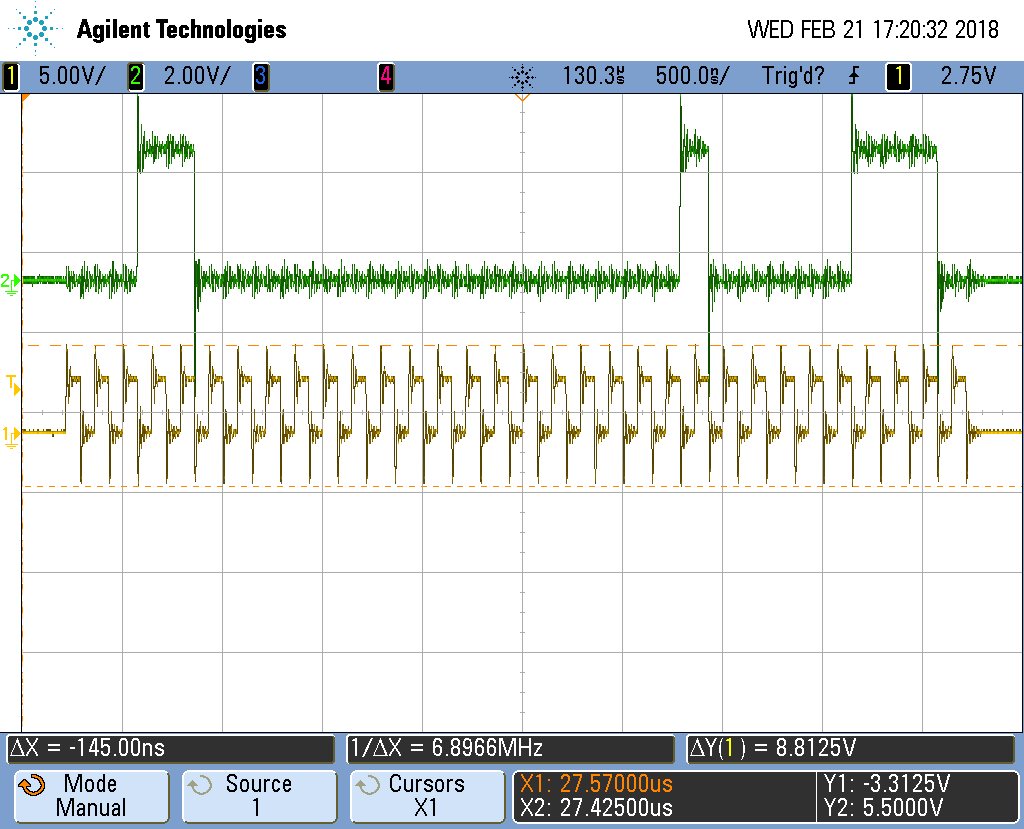

The attachment contains circuit and timing diagram during programming.