Hi Team,

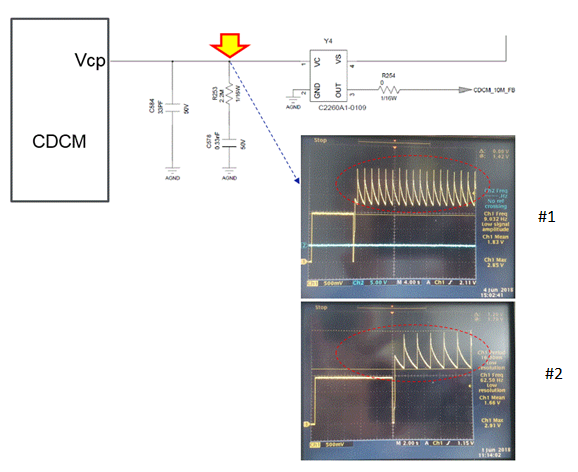

I saw abnormal charge pump voltage scope like as below.

PDF is 80kHz and matched with scope peak period.

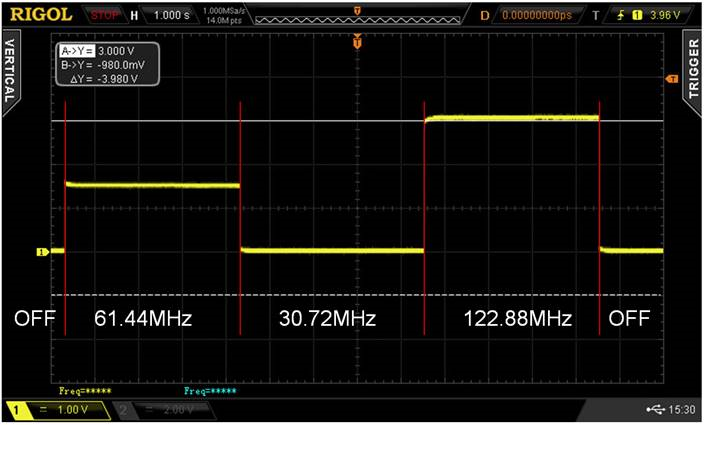

When I measured in EVM, CP voltage scope was different.

In my understand, CP voltage level should be stable when PLL lock. (input 61.44MHz for EVM)

#1 is CDCM7005 PLL unlocked and #2 is CDCM7005 PLL locked correctly.

Frequency is same, but peak amplitude a little bit different.

Why customer board CP voltage level scope is not same as EVM even if PLL locked correctly?

Thank you.

Best Regards,

Jade