Hi team,

I have a question regarding CDC3RL02. Here is my basic setup:

- VBATT = 3.3V

- MCLK = 24MHZ 1.8V CMOS

- LDO = unused/floating

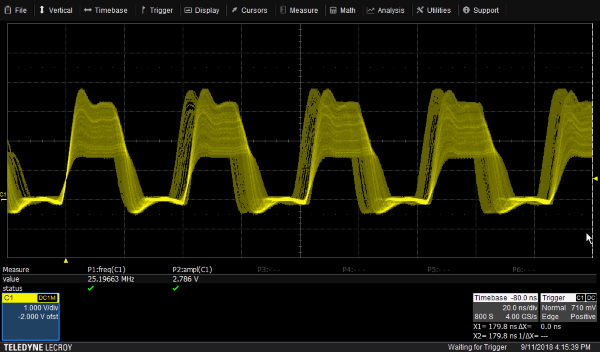

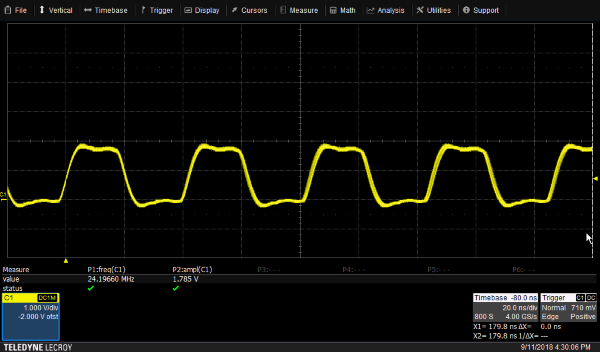

With the above, my output looks like Image 1 (below). However, when I drop VBATT to 1.8V, the output looks like Image 2 (below)--it cleaned up quite a bit. So I have two questions:

- Can I operate at VBATT = 1.8V - are there any potential long-term problems with that approach? This isn't within spec according to the datasheet, but the results look better.

- Is my problem potentially related to the floating LDO? Does the LDO need to be connected to a within-spec capacitor even if it's unused?

Bonus third question - is there anything else that might be causing this problem? Thanks in advance for your help!

1. Output when VBATT = 3.3V (bouncing back and forth between 3.3V and 1.8V)

2. Output when VBATT = 1.8V

Regards,

Brian Angiel