Other Parts Discussed in Thread: DS90LV012A

Hello Team,

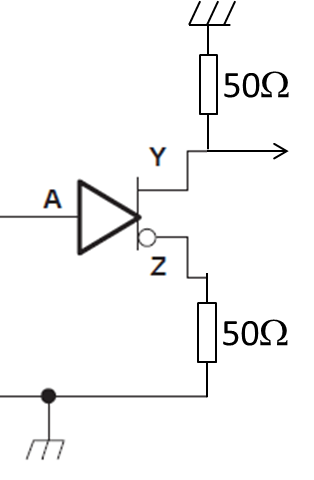

is it possible to use the SN65LVDS104 as a clockdistribution IC for a 25MHz reference clock with two differential and one single ended output where the SE output is connected as shown below?

Can you provide a phase noise plot for a 25MHz carrier, please? Alternatively some phase noise numbers for 25MHz at 1kHz, 10kHz, 100kHz, 1MHz, 10MHz offset would also be ok.

Thanks and Best Regards,

Hans