The PLL output does not look as we expect.

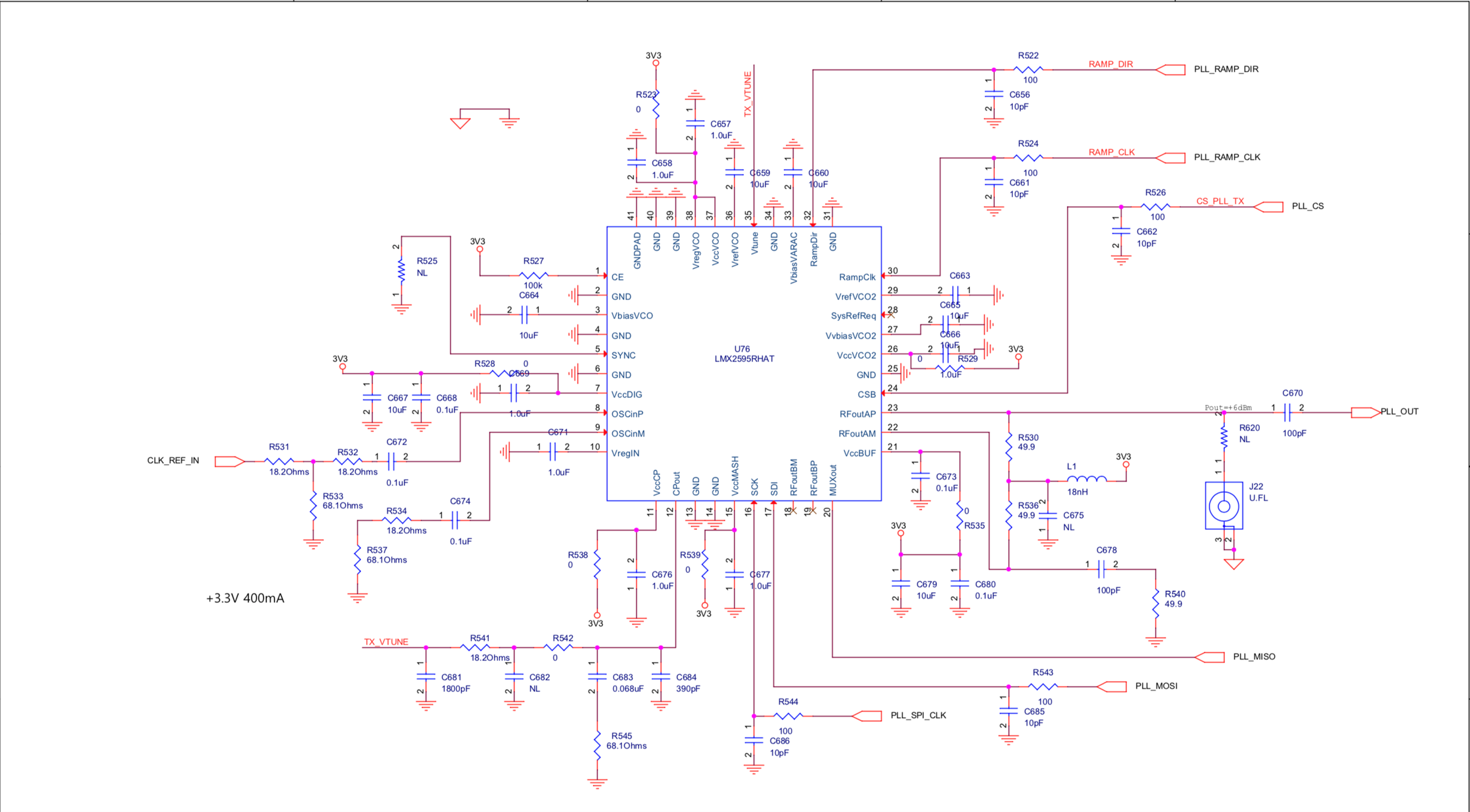

The PLL is reporting that it is locked We are a using a 40 MHz crystal oscillator reference signal in the circuit below. The register values we are using were generated by the PLL API.

Shouldn't the signal be cleaner? Any feedback on the filter topology we are using would be helpful.