Hi,

In my design , CDCE949-Q1 input is a 25MHz cystal, the Y3 output is also 25MHz, which is used for Ethernet PHY. In datasheet, CDCE949-Q1 output clock jitter is Peak-to -Peak period jitter:

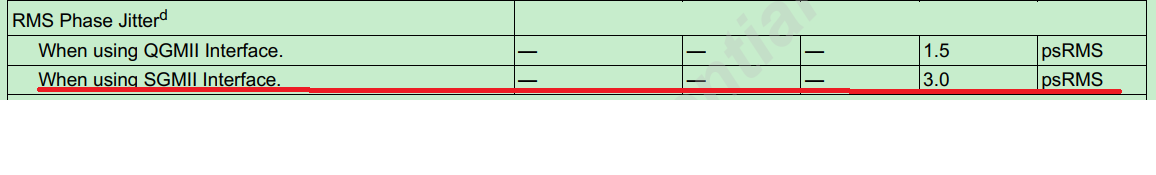

but the Ehternet PHY input clock jitter parameter is RMS phase jitter, which should be <3.0ps

so whether CDCE949-Q1 output phase jitter can meet this requierment? what's the phase jitter value of CDCE949-Q1 output clocks?

Thank you.

Regards.

Gavin