Hi Team,

I would like to get some assistance regarding our customer inquiry with SYSREF timing of LMK04616 since it is not available in the datasheet or any application notes:

Here's the content of the customer's questions:

Assuming the 16-bit divider uses to set CLKout for 100MHz.

When using the channel to act as SYSREF:

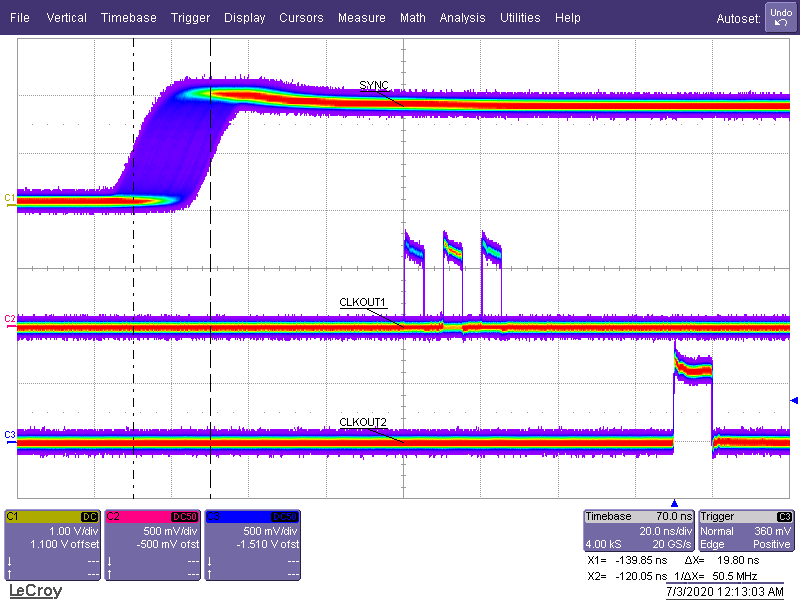

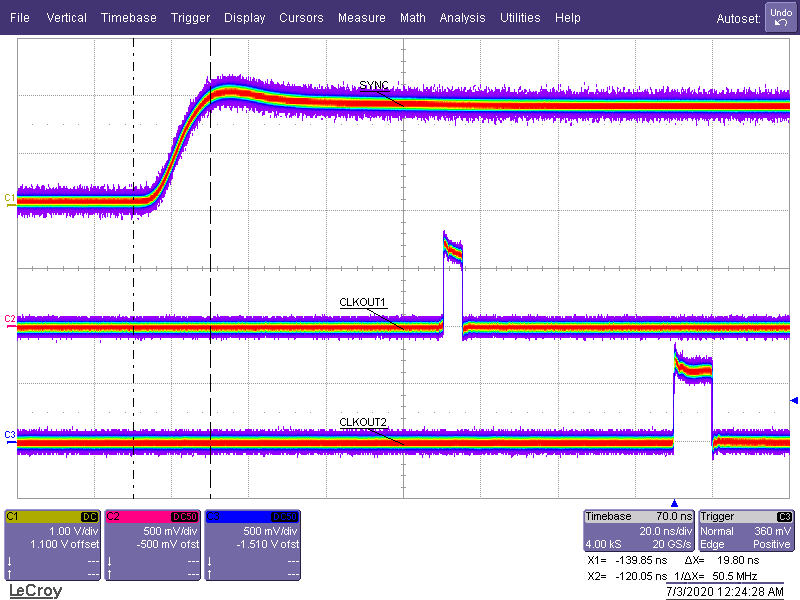

1. What is the SYSREF duration when sysref pulse counter is 1? Is it logic high for 10NSec

2. What is the duration time between external SYNC and the SESREF output?

3. Is it deterministic time?

4. If it is not deterministic time, can I make it deterministic by using some logic at the external SYNC pin?

Assuming one channel uses 100MHz and second channel uses 50MHz (in sync).

1. Can I calculate the time from external SYNC to SYSREF at CLKout1 and SYSREF at CLKout2?

2. Is the time between CLKout1 and CLKout2 will be the same duration every SYSREF request?

3. If the answer is NO, can I make it deterministic by using some logic at the external SYNC pin?

Please let me know if you have any questions to the customer.

Thanks!

Jonathan