Other Parts Discussed in Thread: LMK04906

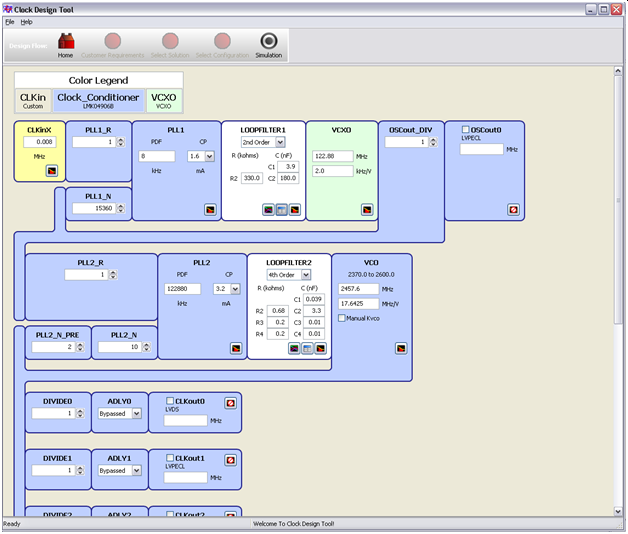

I am evaluating the LMK04906 (using the TI eval board) for the purpose of generating 32.768MHz and 16.384MHz clocks which are sync'ed to the 8KHz timing reference generated by a TI TSB82AA2BI 1394b Link Layer Controller.

The LMK04906 single PLL/internal VCO setup is operational and the LMK04906 successfully locks the output clocks to the 8KHz reference and asserts the Status_LD / PLL2 DLD as long as the LLC is "Master" on the 1394 bus(very little jitter on the 8KHz reference).

However, if this particular PHY is a "Slave" on the 1394 bus (which creates up to 500ns cycle to cycle jitter in the 8KHz reference), the output clocks still achieve lock to the input but the Status_LD / PLL2 DLD output is unstable, changing between locked and unlocked.

Are there any device settings which would stabilize the DLD operation with a jittered reference input ?

Danny