Hi everyone,

I'm working with the LMX2491 PLL at the moment. Recently some problem came up and I was wondering if it has something to do with the start-up procedure of this component but unfortunately, there are no information about the start-up and/or enable times given in the datasheet.

Some more details:

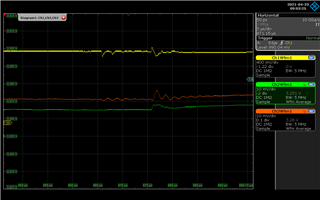

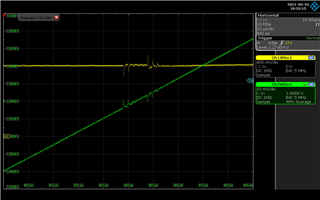

We are using the LMX2491 for an FMCW radar application but see some disturbance on our IF signals. Further investigations showed that these are also visible in the tuning voltage of the VCO, measured at the CPout pin, as can be seen in the scope screen shot below (green curve = tuning voltage, yellow curve = IF signal).

These disturbances appear always at the same time (between 800 µs and 900 µs after the PLL is switched on, varying between exemplars but fixed for one specific). The supply voltage is clean at that time.

For better understanding: We are powering the PLL (or rather the whole RF circuitry) only for short periods. After powering it up the system waits for a PLL lock signal and starts the ramp. After one ramp is sent the system is powered down (Vcc is switched off).

If the PLL is powered continuously, the disturbance only occurs once after the stat-up.

These results led us to the conclusion that there is something happening within the PLL itself. Has anybody some intuition if this could be possible? Is there probably still some start up process going on? Or is there some information about the start-up time of the device?

Thanks, and best regards

Chris