Other Parts Discussed in Thread: PLLATINUMSIM-SW, LMK03318

Hi,

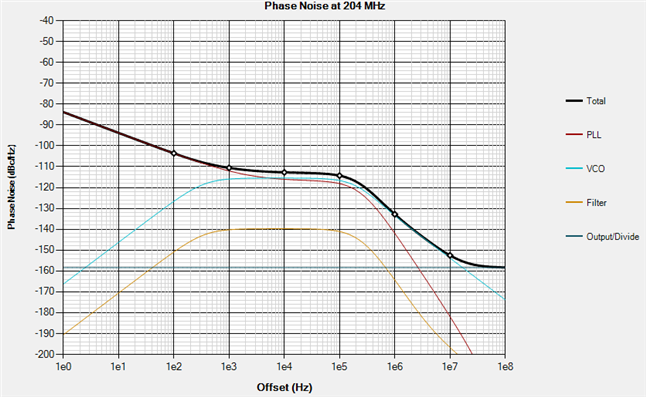

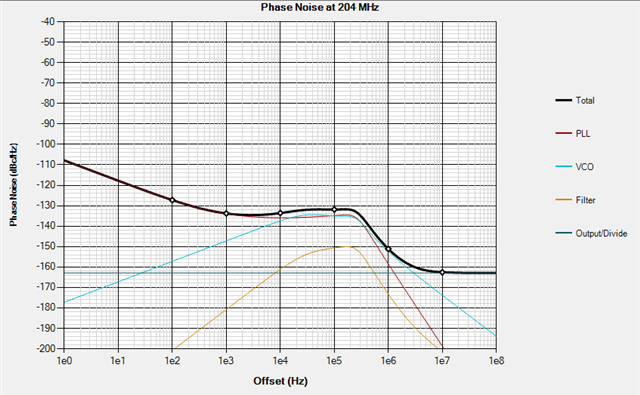

I am using LMK03806 in my design. Design details are as below

FOSCin = 10 MHz

Output frequency to be generated = 204 MHz

I am planning to go with Fvco = 2448 MHz.

Kindly suggest the PLL divider values for the best performance.

Also, elucidate the impact of Phase detector frequency in the overall jitter performance.

Thanks in advance,

Pratiksha