Support Path: /Product/Development and troubleshooting/

Hello,

We have recently purchased the LMX2595 evaluation board.

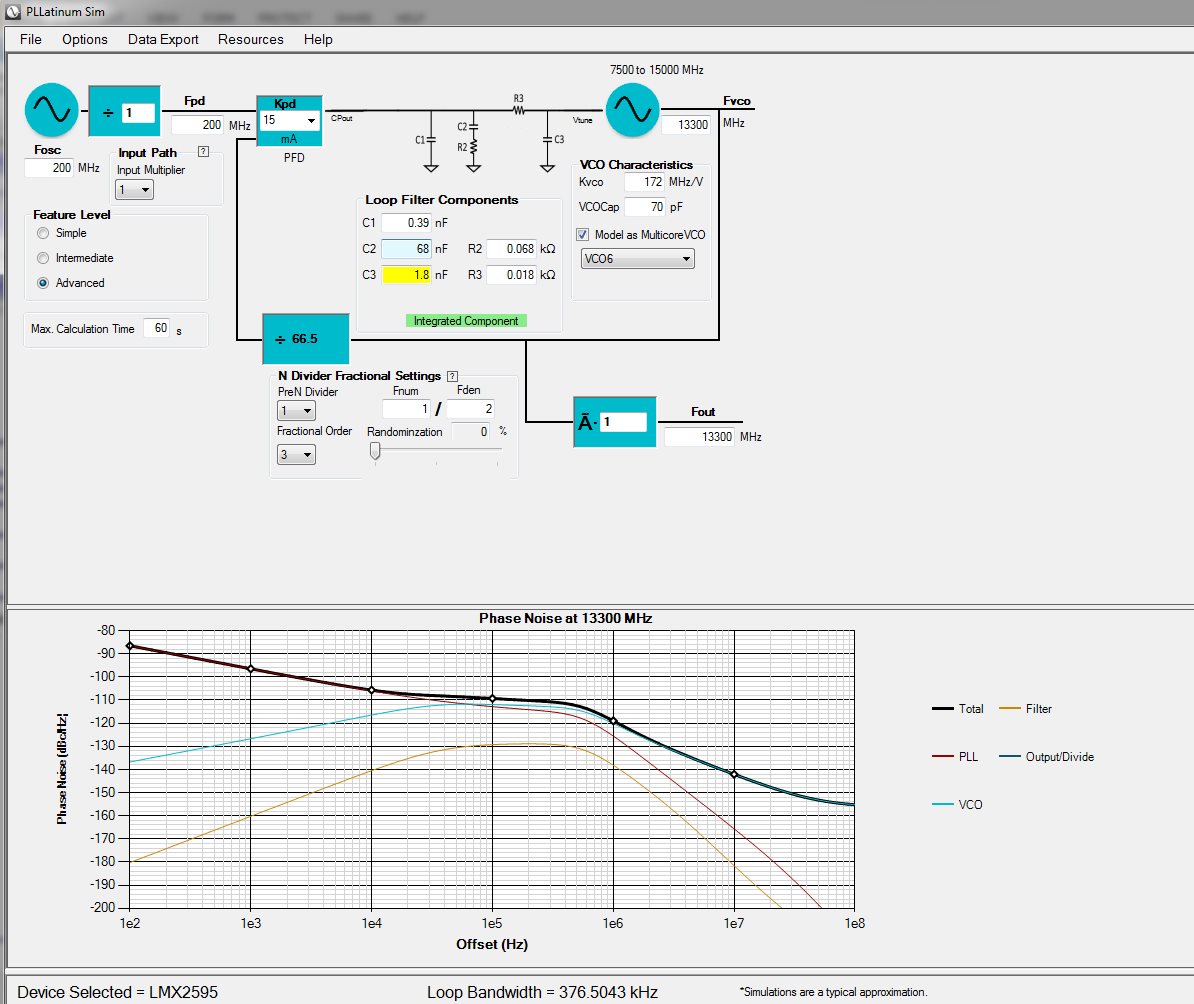

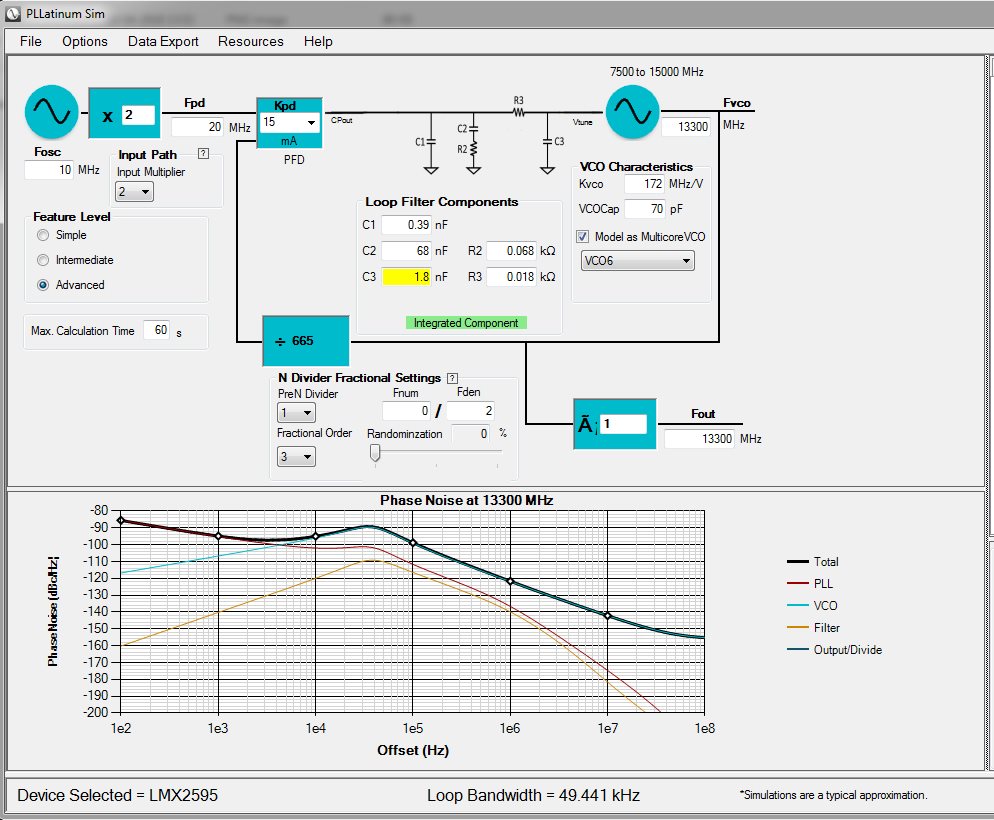

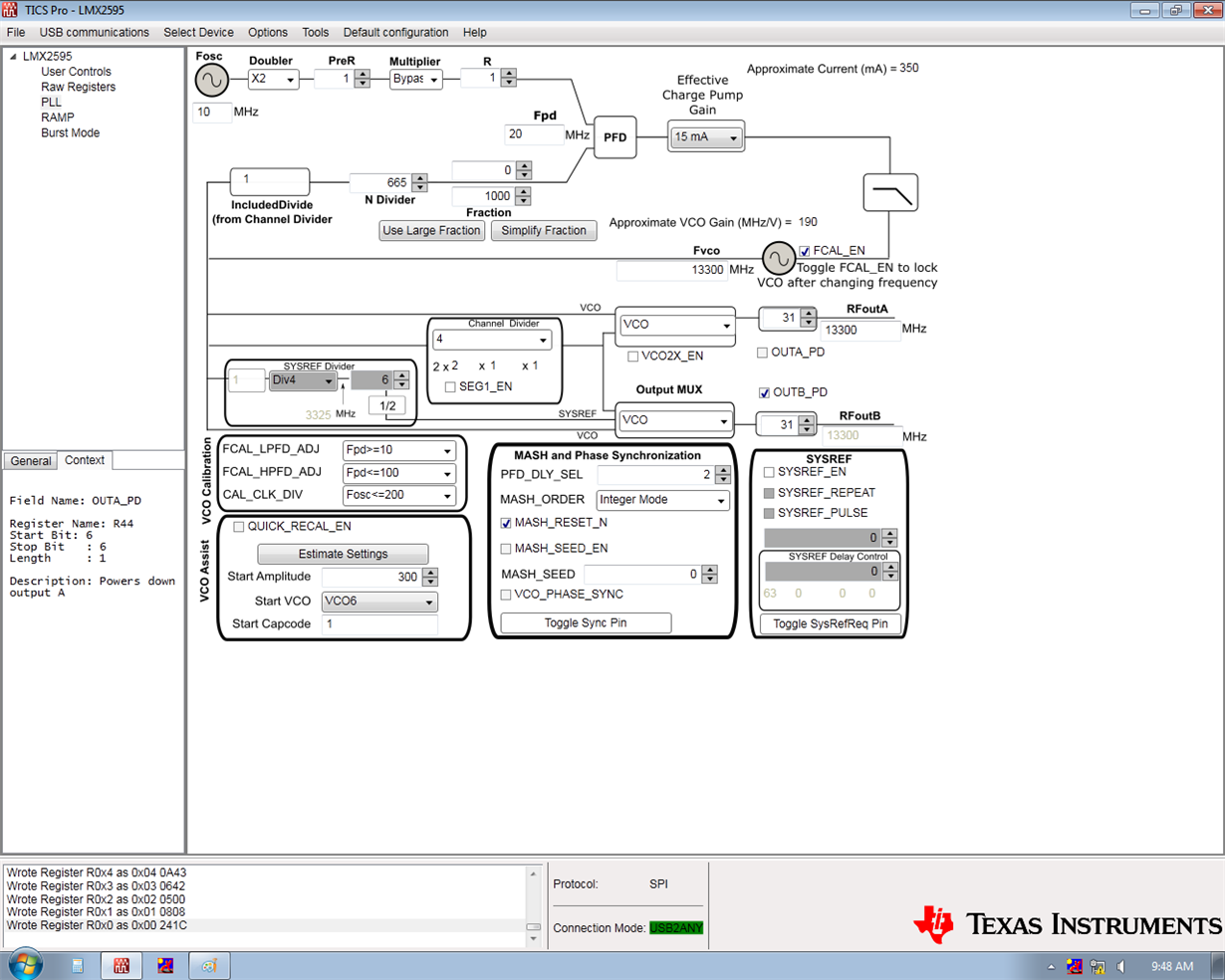

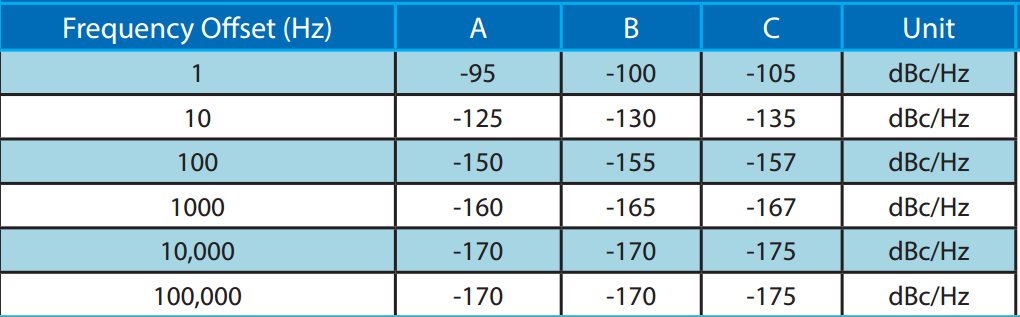

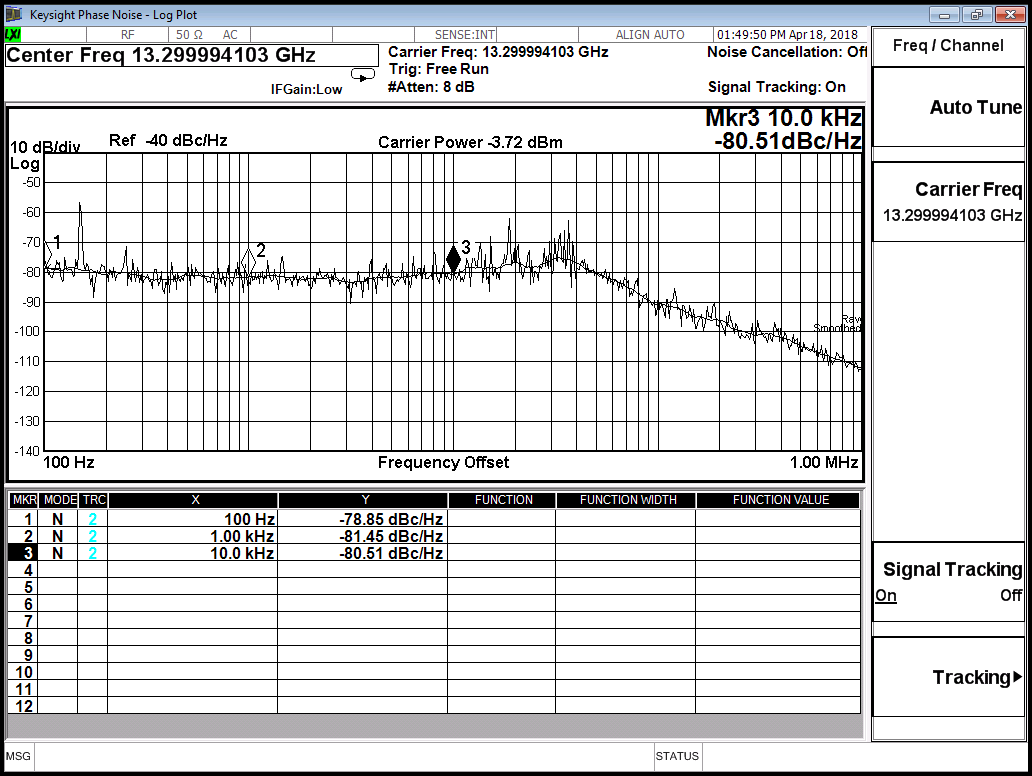

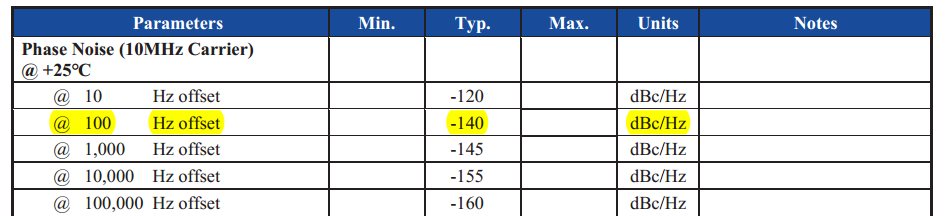

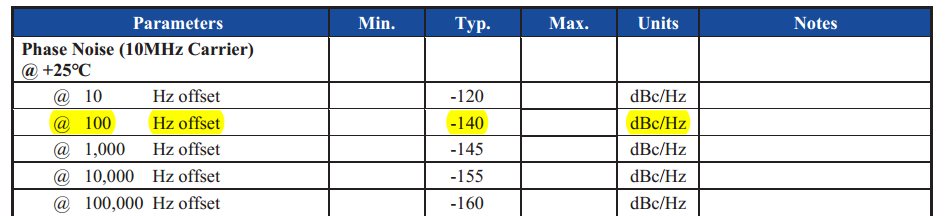

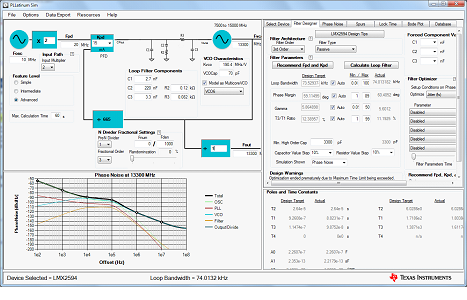

In our application we have a requirement to generate 13GHz with a reference frequency of 10MHz... We have kept PFD to 20MHzusing low noise doubler..We are only measuring a phase noise of -82dB at 10KHz offset.. We are using a very stable OCXO as reference, still we are measuring very high phase noise.... Please advise what could be the problem.... The calculations as per datasheet tells us that the phase noise should be better than -95dB.. Please reply as early as possible.