We run three of these ADCs in sync with each other, on the same CLK signal. Picture 1 shows how each ADC is wired (they are all identical). Strange intermittent readings from the ADCs were what started me on this investigation. Every once in a while, one of the ADCs would produce a reading that I would not expect to see. Throughout my investigation, I found that the DRDY pins of the ADCs get "knocked out of sync." By saying that I mean that the DRDY lines of each ADC will go low at the same time and in sync like they should (picture 2) , until something triggers them to go low about 80ns from each other. The trigger then happens again and they are now 120ns apart (the actual time increment is not important here, just the fact that the DRDY lines get out of sync). This process repeats and the DRDY lines get further and further from each other. Picture 3 shows the DRDY signals from two ADCs out of sync.

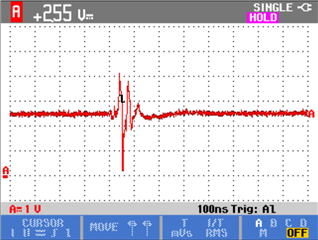

What I have found, and what my team and I believe to be the "out of sync trigger", is a transient voltage spike/dip on the VREFP line. It lasts for around 100ns, spikes the reference voltage past the chip's max voltage limit, and dips pretty low as well. Picture 4 is an example of this VREF transient. We are currently trying to get rid of this transient, but I would still like to get an understanding of your chip and it's synchronization quirks, to know if my theory could be true.

* The VREFP voltage in our circuit is 2.5V, and the transient spikes up to almost 4V. The max voltage on the VREFP line is 3.3V as per the datasheet. Could this violation cause the ADCs to lose their synchronization?

* The transient also dips the VREF voltage to almost 1V, could this be causing the ADCs to somehow reset, therefore losing their sync?

* Could these strange readings be a symptom of the Out-of_range system monitor from section 8.3.5 of the datasheet instead of synchronization loss?

Whatever the cause of this out-of-sync event is, I have found a 'band-aid' solution with software. By periodically taking the start pin of all 3 ADCs low and then high again, the DRDY signals snap back in sync. The out of sync trigger event still happens, and the DRDY signals still periodically get out of sync from it, but they snap back into synchronization before any problems arise. This solution was found by reading section 8.4.3 of the datasheet, and I made sure the timing requirement tw(STL) is satisfied from table 13.

With this band-aid in place, the ADCs can run for many hours without producing any strange readings. I have yet to see any strange readings thus far.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.