Hi,

I have a ADS131M04 in the evaluation board and it seems that is not respondig to the configuration change.

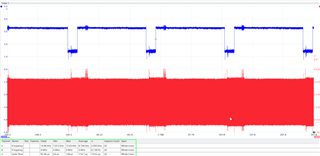

I change the OSR inside the CLOCK register and it doesn't change the time between DRDY(high to low). After I write the register I read it and I can see that the value in the register is the one I set.

Also I am setting the SYNC/RESET signal down for 2ms with a CLKIN of 8MHz and the reset is not doing anything. After the RESET the device is not returning the 0xFF24 and the device continues in LOCK status.

Apart from that the ADC data I receiving is all zeros, the frame I am receiving is "81 00 00 00 00 00 00 00 00 00 00 00 00 00 00 b4 2d 00" with a word size of 24bits. The CRC is correct but I don't understand why all the values are 0.

Do you know what could be happening?

Regards,

Iñaki